# Development and Assessment of Engineering Design Competencies using Technology-Enhanced-Learning Environment

Submitted in partial fulfilment of the requirements of the degree of

Doctor of Philosophy

by

Madhuri Mavinkurve

Roll no: 10438803

Supervisor:

Sahana Murthy (IIT Bombay)

Inter-Disciplinary Program in Educational Technology

INDIAN INSTITUTE OF TECHNOLOGY BOMBAY

2016

## **Dedication Sheet**

Dedicated

То

My husband Mr.K.S.Mavinkurve, my teachers and Almighty

# **Approval Sheet**

### Abstract

Engineering is a practice-driven profession. Engineering graduates should be able to demonstrate and apply thinking skills in addition to their domain knowledge. Engineering design thinking skill is one such important thinking skill. Even though this skill is being taught using various instructional methods such as project based learning, it is reported that students are unable to demonstrate engineering design thinking skill. A key challenge is in defining what to teach as engineering design thinking, and how to assess this skill.

In this thesis, we address the problem of developing and assessing engineering design thinking skill among undergraduates. In our solution approach, we operationalized engineering design thinking skill in terms of measurable competencies. We identified the following engineering design competencies: Structure Open Problem, Multiple Representation, Information Gathering, Convergent Thinking and Divergent Thinking. We developed rubrics as a formative assessment instrument for these competencies. The rubrics assess students' progress of competency acquisition as well as provide constructive feedback to attain competency in a given design task.

To help students attain the engineering design competencies, we designed TELE-EDesC - Technology Enhanced Learning Environment for Engineering Design Competency. TELE-EDesC is a self-learning environment which includes interactive learning activities, referred to as 'Learning Dialogs'. TELE-EDesC Learning Dialogs harness the affordances of modern technology such as interactive experimentation, self-regulation, and personalized feedback, to trigger essential metacognitive processes required for engineering design thinking.

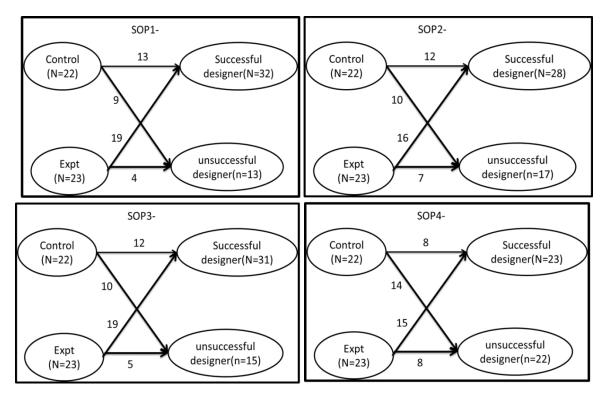

We developed TELE-EDesC learning modules for Structure Open Problem (SOP) competency for topics in analog electronics, and tested them using quasi-experimental studies (N=295) as well as qualitative interaction analysis, with second year engineering students. We found that TELE-EDesC was effective for learners in attaining SOP competency (statistically significant differences, p<0.01). From the interaction analysis, we identified productive learning behaviours of successful students and revised TELE-EDesC to promote such behaviour among all learners.

The main contributions of this thesis are: TELE-EDesC learning modules that have been empirically validated for SOP competency for a range of topics in analog electronics, a pedagogical framework to develop TEL environments for engineering design competencies, and assessment rubrics for engineering design competencies.

*Key words:* Engineering Design Competencies, Rubrics, Structure Open Problem, Technology Enhanced Learning Environment, TELE-EDesC, Learning Dialogs, Pedagogical framework

## Content

| Dedication Sheetii                                                      |

|-------------------------------------------------------------------------|

| Approval Sheetiii                                                       |

| Abstractiv                                                              |

| Contentv                                                                |

| List of Figuresxii                                                      |

| List of Tablesxv                                                        |

| Abbreviation Notation and Nomenclaturexvii                              |

| Declaration Sheetxviii                                                  |

| Chapter 11                                                              |

| Introduction1                                                           |

| 1.1. Problem statement                                                  |

| 1.2. Solution overview                                                  |

| 1.2.1. Motivation for solution                                          |

| 1.2.2. TELE-EDesC: TEL Environment for Engineering Design Competencies4 |

| 1.2.3. Approach to designing solution                                   |

| 1.3. Methodology                                                        |

| 1.4. Delimitations of the thesis                                        |

| 1.4.1. Scope of content9                                                |

| 1.4.2. Scope of design competencies10                                   |

| 1.4.3. Scope of design problem type11                                   |

| 1.5. Contributions of the thesis                                        |

| 1.6. Organization of the thesis                                         | 13 |

|-------------------------------------------------------------------------|----|

| Chapter 2                                                               | 15 |

| Literature Review                                                       | 15 |

| 2.1. Organisation of literature review                                  | 15 |

| 2.2. Problem space – What is engineering design thinking?               | 16 |

| 2.2.1. Defining engineering design thinking                             | 17 |

| 2.2.2. Methods to teach engineering design                              | 18 |

| 2.2.3. Engineering design as a thinking skill                           | 21 |

| 2.2.4. From synthesis of literature to problem definition               | 24 |

| 2.2.5. Literature review towards a solution approach – an overview      | 29 |

| 2.3. Assessment of engineering design                                   | 30 |

| 2.3.1. Assessing design products and processes                          |    |

| 2.3.2. Rubrics as an assessment instrument                              | 31 |

| 2.3.3. Need for new assessment instrument                               | 33 |

| 2.4. Teaching-learning of thinking skills                               | 34 |

| 2.4.1. Ill-structured problem solving                                   | 34 |

| 2.4.2. Inquiry learning                                                 | 35 |

| 2.4.3. Decision-making                                                  | 36 |

| 2.4.4. Summary and implications of teaching-learning of thinking skills | 37 |

| 2.5. Technology Enhanced Learning (TEL) Environments                    |    |

| 2.5.1. TEL environments for thinking skills                             |    |

| 2.5.2. Design principles of TEL environments                            | 42 |

| 2.5.3. Research questions arising from literature review                | 44 |

| Chapter 3                                                               | 47 |

| Research Method                                                         | 47 |

| 3.1. Problem analysis phase                                                         | 48   |

|-------------------------------------------------------------------------------------|------|

| 3.2. Design prototype phase                                                         | 49   |

| 3.3. Evaluation and refinement phase                                                | 51   |

| 3.4. Ethical considerations                                                         | 53   |

| 3.5. Summary                                                                        | 54   |

| Chapter 4                                                                           | 55   |

| Rubrics: Operationalization and assessment of engineering design competencies       | 55   |

| 4.1. Research Design: Exploratory sequential mixed method                           | 56   |

| 4.1.1. Step 1: Qualitative method to identify engineering design competencies       | 57   |

| 4.1.2. Step 2: Building on qualitative results to design assessment instrument      | 58   |

| 4.1.3. Step 3: Quantitative method to establish validity, reliability and usability | y of |

| assessment instrument                                                               | 58   |

| 4.1.4. Step 4: Interconnection of results                                           | 60   |

| 4.2. Identifying measurable units of engineering design competencies                | 60   |

| 4.2.1. Breaking up of a design competency into sub-competencies                     | 61   |

| 4.3. Constructing rubrics to assess engineering design competencies                 | 63   |

| 4.4. Establishing validity and reliability of rubrics                               | 66   |

| 4.4.1. Types of validity and reliability                                            | 66   |

| 4.4.2. Content validity                                                             | 68   |

| 4.4.3. Construct validity - Response Process                                        | 69   |

| 4.4.4. Construct validity – Criterion validity                                      | 71   |

| 4.4.5 Generalizability                                                              | 72   |

| 4.4.6 Reliability                                                                   | 73   |

| 4.5. Implementation of rubrics and usability                                        | 75   |

| 4.5.1. Rubrics used to assess student design solutions                              | 75   |

| 4.5.2. Usability of rubrics by teachers                                             | 77   |

| 4.6. Interpretation of rubrics scores: competency achievement        | 77  |

|----------------------------------------------------------------------|-----|

| 4.7. Summary                                                         |     |

| Chapter 5                                                            | 82  |

| Development of TELE-EDesC Learning Environment                       | 82  |

| 5.1. Research method                                                 | 83  |

| 5.2. Analysis of experts' design solution for SOP competency         |     |

| 5.3. Instructional strategies for triggering metacognitive processes |     |

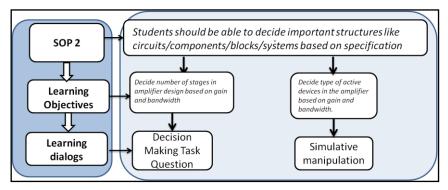

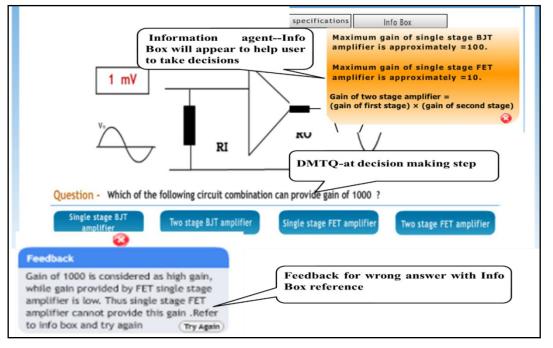

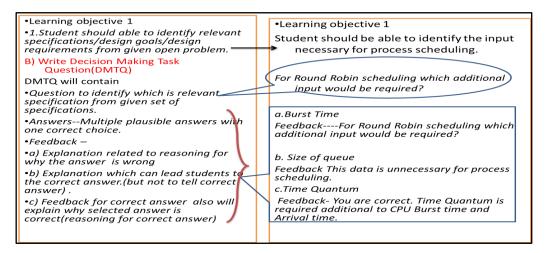

| 5.3.1. Instructional strategies for 'decision-making'                |     |

| 5.3.2. Instructional Strategies for 'concept integration'            |     |

| 5.3.3. Instructional Strategies for 'synthesis'                      |     |

| 5.4. Design of Learning Dialogs                                      | 90  |

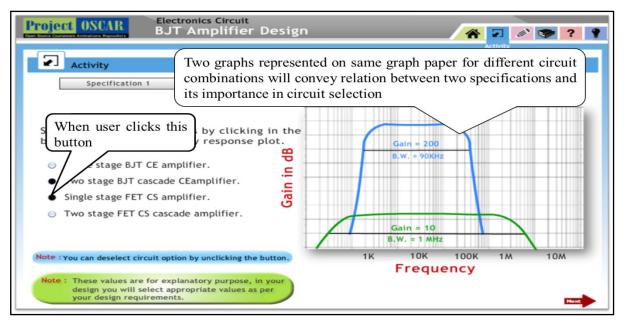

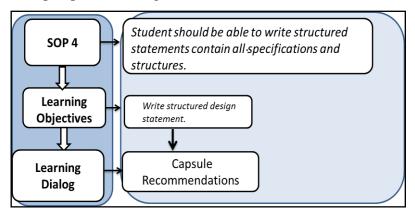

| 5.4.1. Learning Dialogs for SOP competency                           | 91  |

| 5.5. Framework for developing TELE-EDesC                             | 96  |

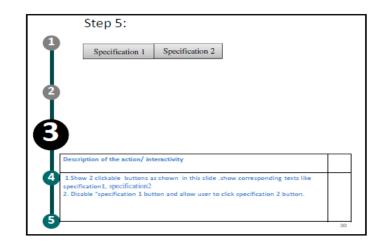

| 5.5.1 Guidelines for creating TELE-EDesC Learning Dialogs for SOP    | 99  |

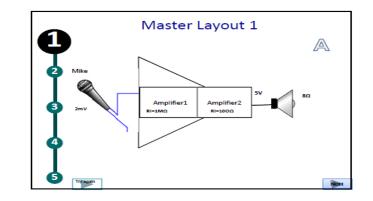

| 5.6. Example of development of TELE-EDesC modules                    |     |

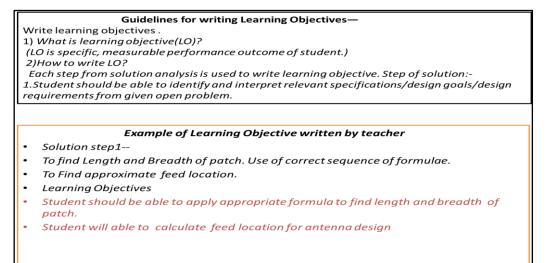

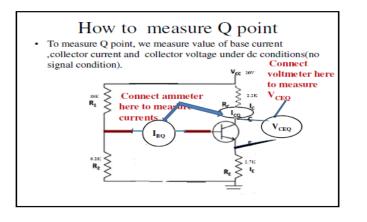

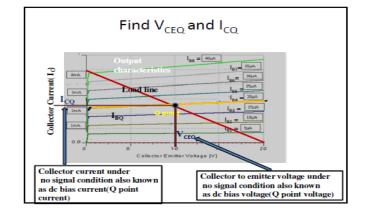

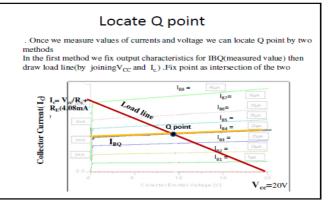

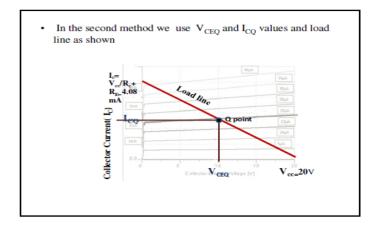

| 5.6.1. Content preparation phase                                     | 101 |

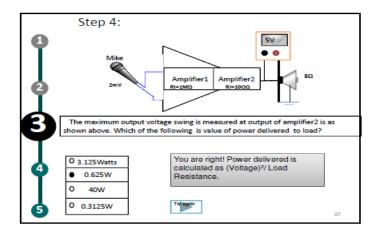

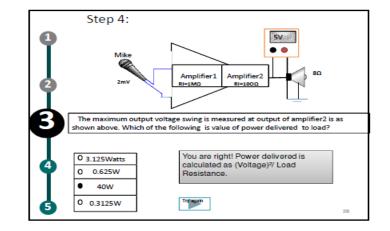

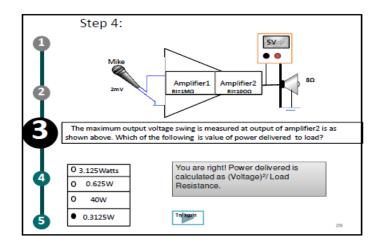

| 5.6.2. Design of Learning Dialogs for SOP Competency                 | 103 |

| 5.6.3. TELE-EDesC modules in analog electronics domain               | 111 |

| 5.7. Summary                                                         | 113 |

| Chapter 6                                                            | 114 |

| Evaluation of TELE-EDesC                                             | 114 |

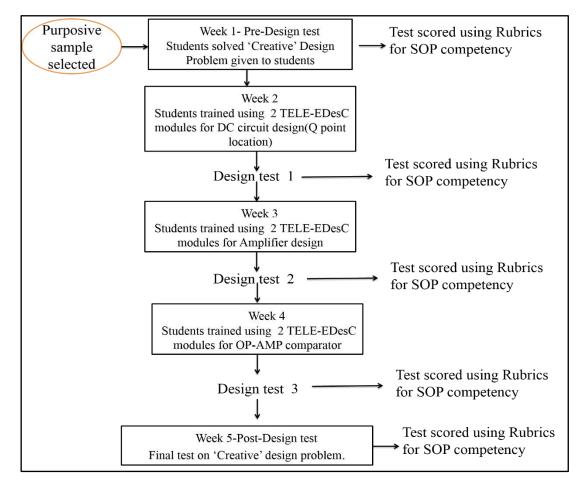

| 6.1. Quantitative method research design                             | 115 |

| 6.1.1. Participants                                                  | 115 |

| 6.1.2. Materials and procedure                                       | 116 |

| 6.1.3. Instrument                                                    | 118 |

| 6.1.4. Data Analysis techniques                                                    |

|------------------------------------------------------------------------------------|

| 6.2. Results of quantitative method: Learning effectiveness                        |

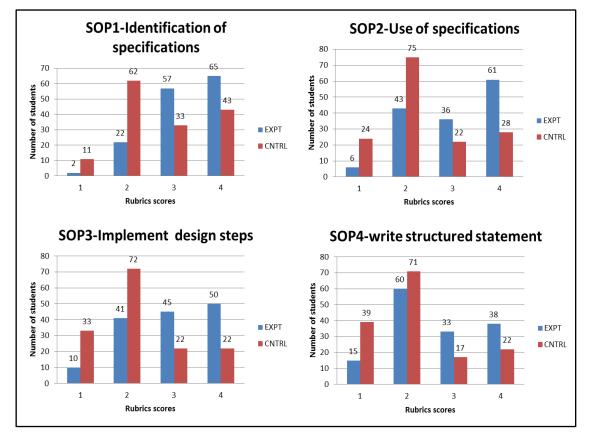

| 6.2.1. Comparing TELE-EDesC group and control group on SOP post-test121            |

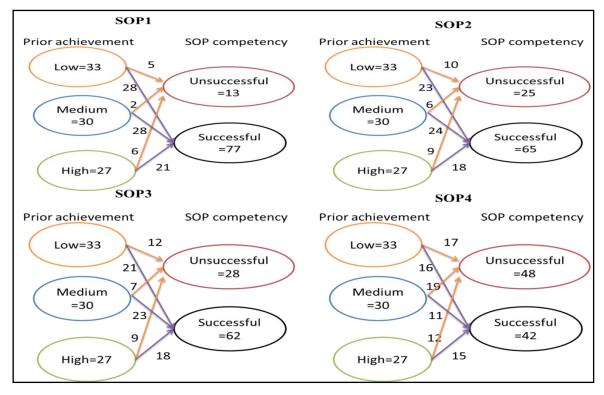

| 6.2.2. Role of prior content knowledge in attainment of SOP competency             |

| 6.2.3. Identification of successful students from achievers category for each sub- |

| competency127                                                                      |

| 6.2.4. Summary of learning effectiveness results from quantitative strand129       |

| 6.3. Explaining quantitative results: designing the qualitative study              |

| 6.3.1. Participants and procedure                                                  |

| 6.3.2. Data coding                                                                 |

| 6.3.3. Data analysis techniques132                                                 |

| 6.4. Results of qualitative study                                                  |

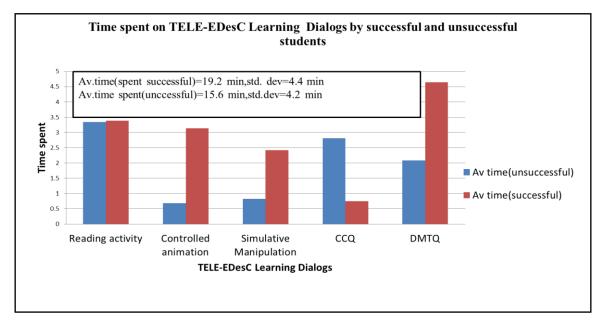

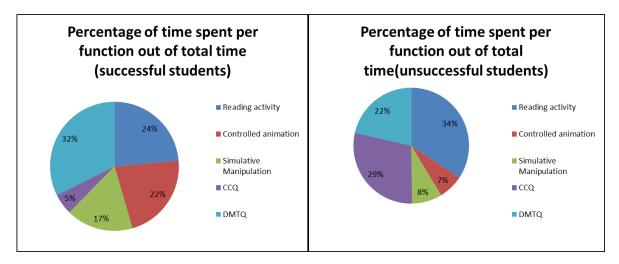

| 6.4.1. Time spent on Learning Dialogs                                              |

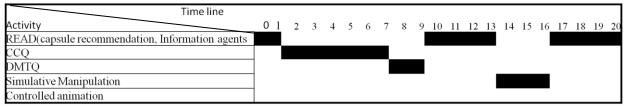

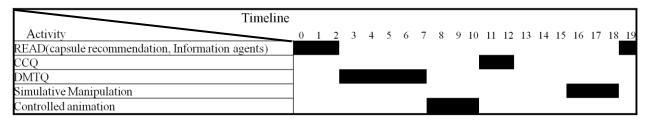

| 6.4.2. Chronological representation of learning behaviour134                       |

| 6.4.3. Discussion of qualitative study results136                                  |

| 6.5. Discussion                                                                    |

| 6.6. Summary                                                                       |

| Chapter 7                                                                          |

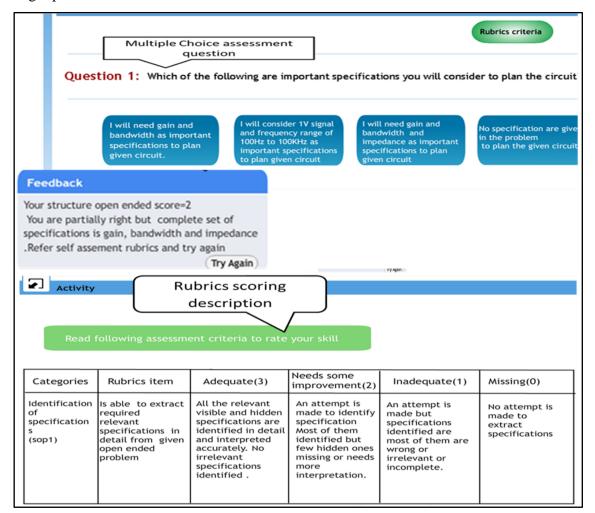

| Refining TELE-EDesC via self-assessment rubrics140                                 |

| 7.1. Theoretical basis for refinement of TELE-EDesC                                |

| 7.2. Refined TELE-EDesC                                                            |

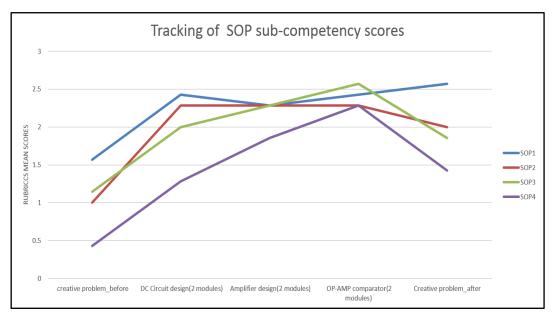

| 7.3. Learning effectiveness of refined TELE-EDesC144                               |

| 7.3.1. Learning effectiveness for attainment of SOP4144                            |

| 7.3.2. Data analysis and results145                                                |

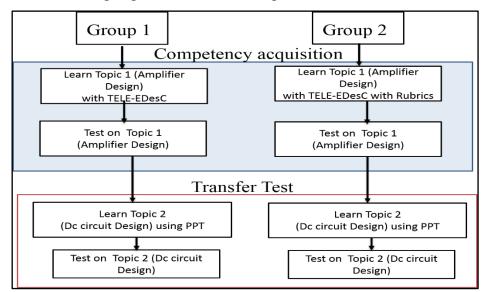

| 7.4. Transfer of competency to new topic                                           |

| 7.4.1. Methodology                                                                 |

| 7.4.2. Data analysis and results                                                          | 150  |

|-------------------------------------------------------------------------------------------|------|

| 7.5. Summary                                                                              | 152  |

| Chapter 8                                                                                 | 154  |

| Extension of TELE-EDesC                                                                   | 154  |

| 8.1. Development of TELE-EDesC modules for SOP in new domains                             | 155  |

| 8.2. Application of pedagogical framework to develop TELE-EDesC for variou competencies   |      |

| 8.3. TELE-EDesC to develop SOP for Creative level design problems                         | 174  |

| 8.4. Summary                                                                              |      |

| Chapter 9                                                                                 |      |

| Discussion and Conclusion                                                                 | 182  |

| 9.1. Overview of problem and solution                                                     |      |

| 9.2. Answering Research Questions                                                         |      |

| 9.3. Generalisability of TELE-EDesC                                                       | 189  |

| 9.4. Contribution of thesis                                                               | 191  |

| 9.5. Limitations                                                                          | 194  |

| 9.6. Future Work                                                                          | 196  |

| 9.6.1. Expansion of pedagogical framework to develop TEL environments for thinking skills |      |

| 9.6.2. Collaborative learning of engineering design competencies                          | 197  |

| 9.6.3. Establishing Rubrics utility for other branches of engineering                     | 198  |

| Appendix                                                                                  |      |

| Appendix-I                                                                                | 200  |

| Table A1.1: Analysis of research papers for mapping engineering design competencie        | s200 |

| Table A1.2: Rubrics to assess Engineering Design Competencies                             |      |

| Appendix-II                                                                               | 215  |

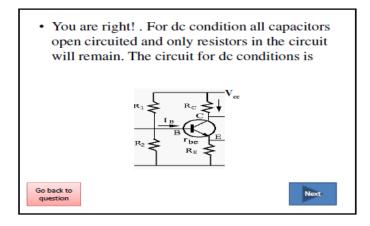

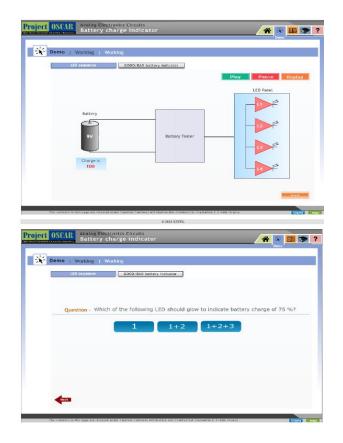

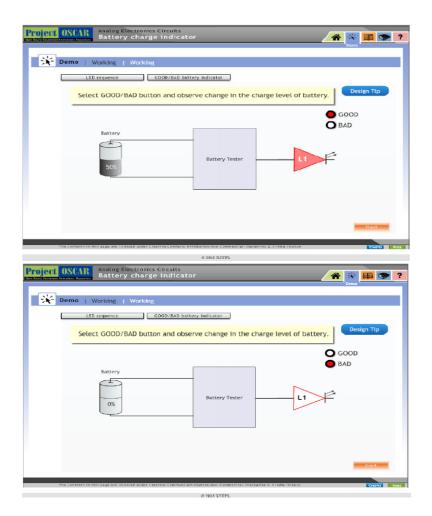

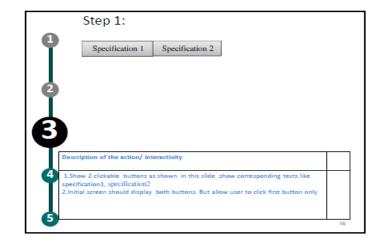

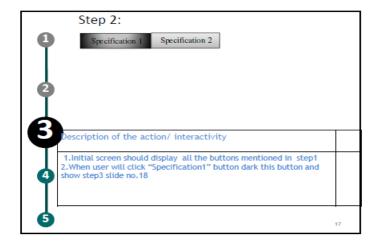

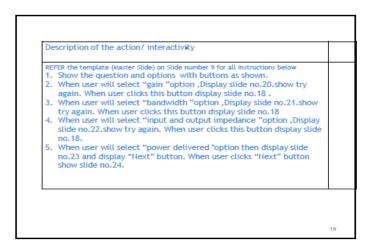

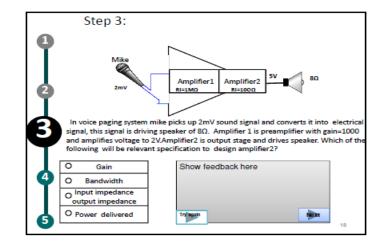

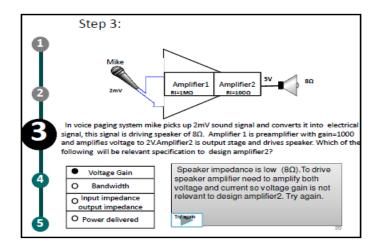

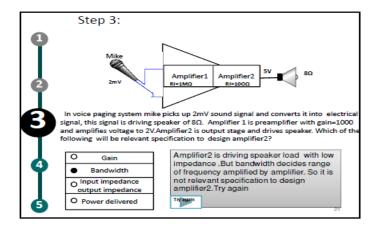

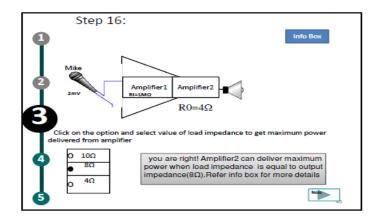

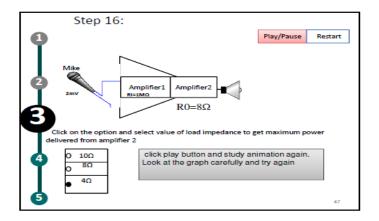

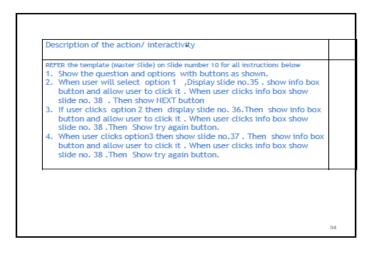

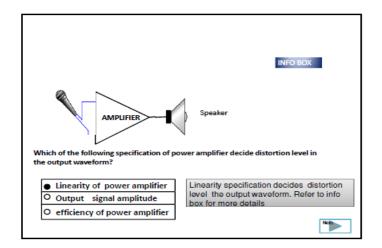

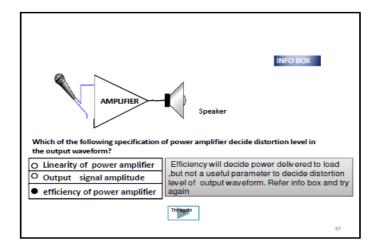

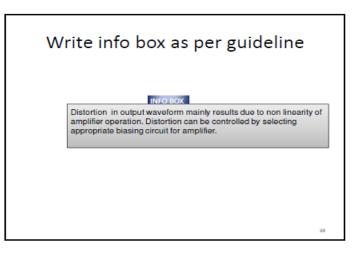

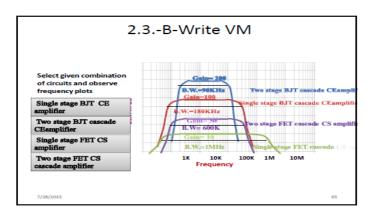

| Screenshots of TELE-EDesC Learning Material                                       | 215 |

|-----------------------------------------------------------------------------------|-----|

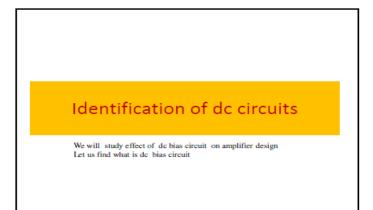

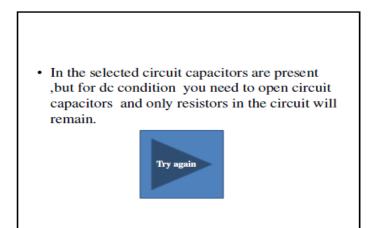

| 2.1. Modules 1 and 2 - DC circuit design                                          | 215 |

| 2.2. Modules 3 and 4 - Amplifier Design                                           | 227 |

| 2.3. Modules 5 and 6 - OP-AMP comparator design                                   | 234 |

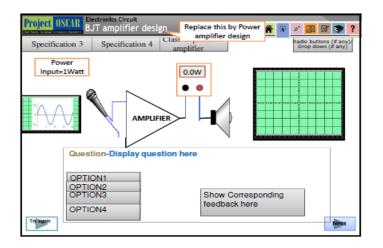

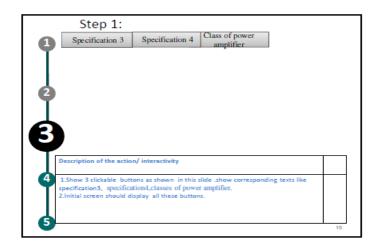

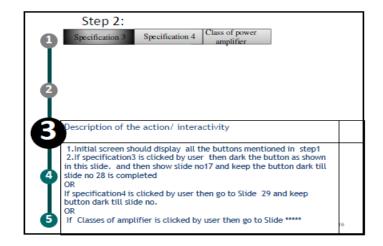

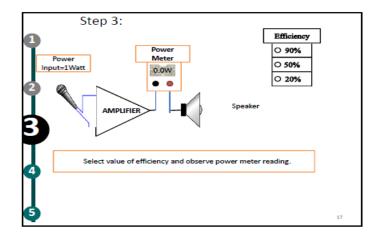

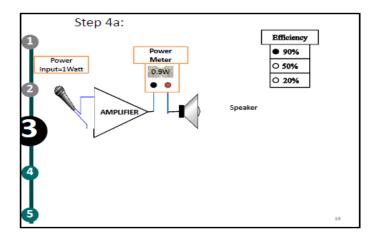

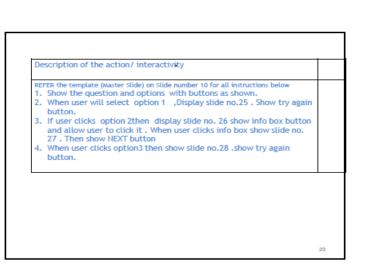

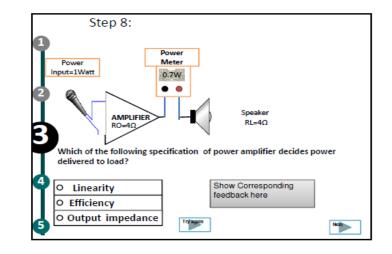

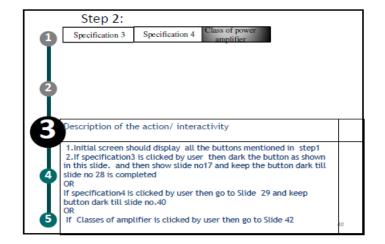

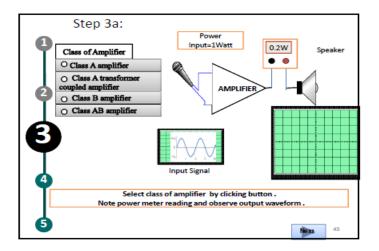

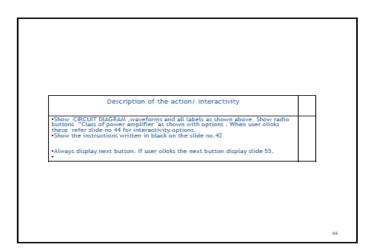

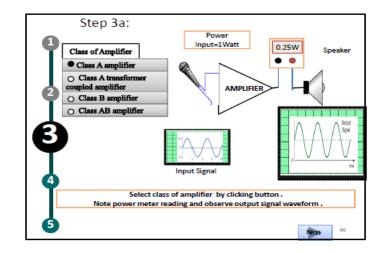

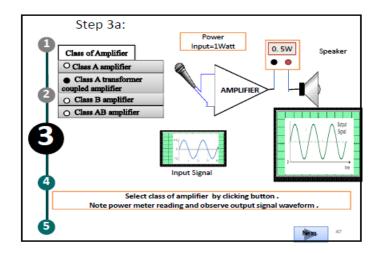

| 2.4. Modules 7 and 8 - Power amplifier design (Instructional Design Document-IDD) | 236 |

| Appendix-III                                                                      | 261 |

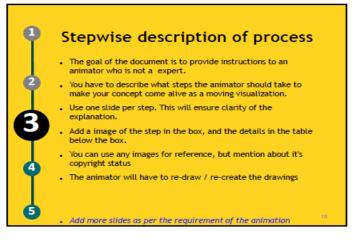

| Template for writing TELE-EDesC                                                   | 261 |

| 3.1. Template for writing TELE-EDesC                                              | 261 |

| 3.2. Template to develop TELE-EDesC applied by teacher 1-Scheduling algorithm     | 276 |

| 3.3. Template to develop TELE-EDesC applied by teacher 2-Antenna design           | 289 |

| References                                                                        | 294 |

| List of Publications                                                              | 315 |

| Acknowledgements                                                                  | 317 |

# **List of Figures**

| Fig.  | g. 1.1. Learning Dialogs of TELE-EDesC        | 2                                                 | 1 |

|-------|-----------------------------------------------|---------------------------------------------------|---|

| Fig.  | g. 1.2. Steps of solution approach            |                                                   | 5 |

| Fig.  | g. 1.3. Overview of Research Methodolog       | y (EDR)                                           | 7 |

| Fig.  | g. 1.4. Thesis chapters' organisation and co  | onnections14                                      | 4 |

| Fig.  | g. 2.1. Organisation of related work          |                                                   | 5 |

| Fig.  | g. 2.2. Summary of literature review of pro   | blem space                                        | ) |

| Fig.  | g. 2.3. Learning environment and instruction  | onal strategies for developing thinking skills 38 | 3 |

| Fig.  | g. 2.4. Organisation of related work in solu  | tion space45                                      | 5 |

| Fig.  | g. 2.5. Outcomes of literature review leadi   | ng to research questions46                        | 5 |

| Fig.  | g. 3.1. Overview of Education Design Res      | earch Method (reproduced from chapter 1 fig 1.3)  | ) |

| ••••• |                                               |                                                   | 3 |

| Fig.  | g. 3.2. Steps of design prototype phase of l  | EDR51                                             | 1 |

| Fig.  | g. 3.3. Evaluation and refinement phase of    | EDR                                               | 3 |

| Fig.  | g. 4.1. Steps of exploratory sequential mix   | ed research design56                              | 5 |

| Fig.  | g. 4.2. Part of content analysis from sampl   | e solution of expert62                            | 2 |

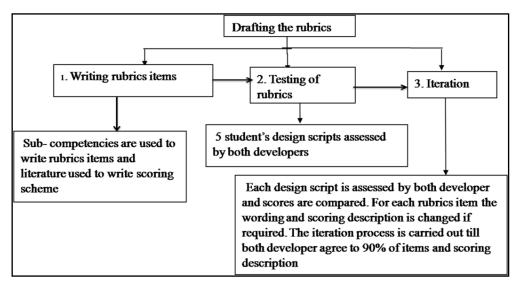

| Fig.  | g. 4.3. Flowchart for writing rubrics         |                                                   | 1 |

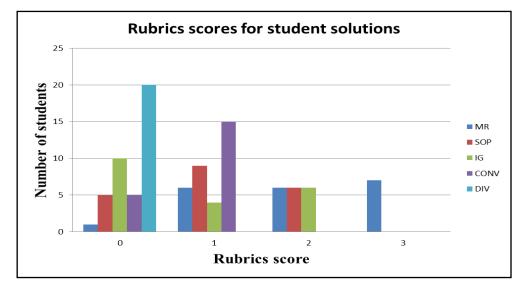

| Fig.  | g. 4.4. Rubrics scores of students' solution  | s70                                               | ) |

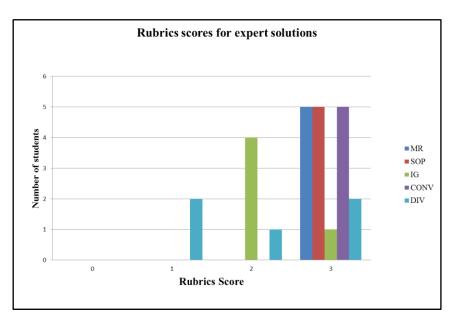

| Fig.  | g. 4.5. Rubrics scores of experts' solution   |                                                   | 1 |

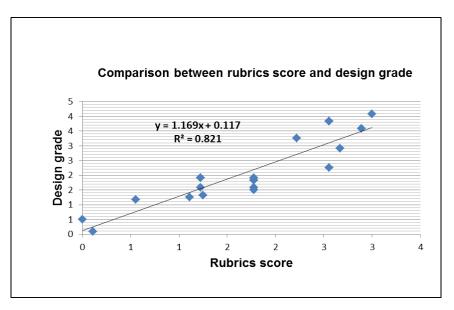

| Fig.  | g. 4.6. Relation between design grade and     | rubrics scores72                                  | 2 |

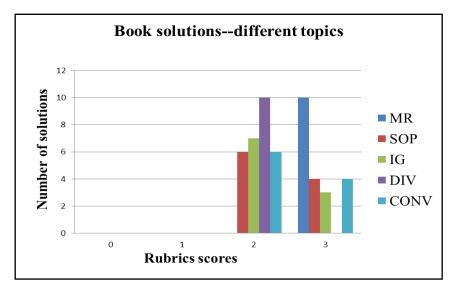

| Fig.  | g. 4.7. Rubrics score for different topics    |                                                   | 3 |

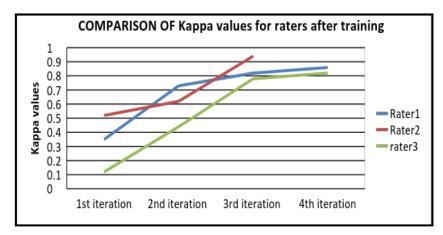

| Fig.  | g. 4.8. Variation in Kappa for three raters a | as training progresses75                          | 5 |

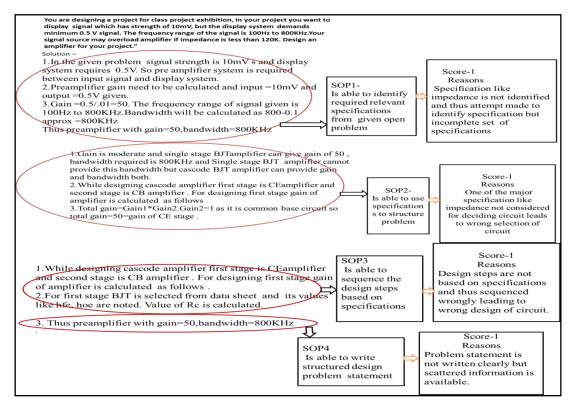

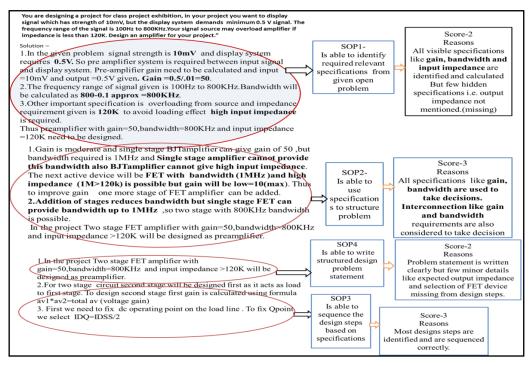

| Fig.  | g. 4.9. Rubrics scores of an unsuccessful d   | esign ("poor solution")76                         | 5 |

| Fig.  | g. 4.10. Rubrics scores of a successful desi  | gn ("good solution")76                            | 5 |

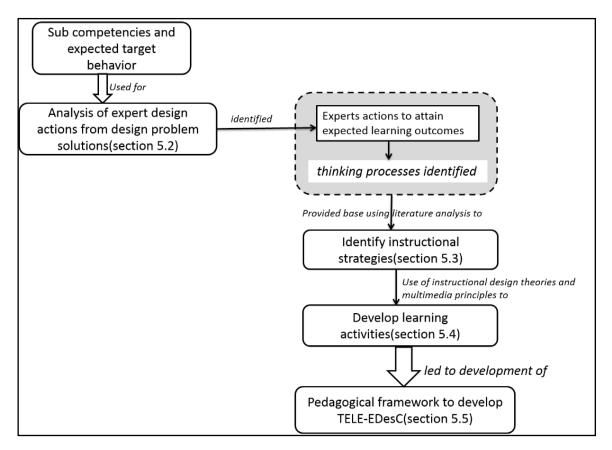

| Fig.  | g. 5.1. Research method for TELE-EDesC        | development (reproduced from Chapter 3) 84        | 1 |

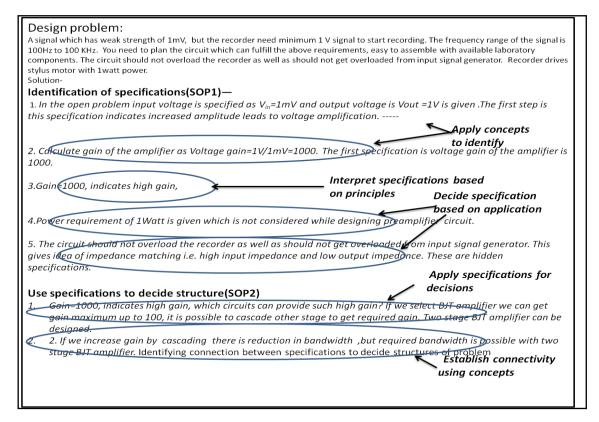

| Fig.  | g. 5.2. Example of content analysis of an e   | xpert's design actions, sub-competency wise86     | 5 |

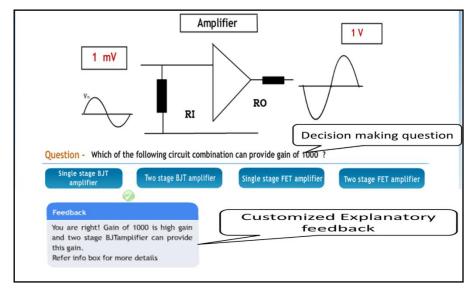

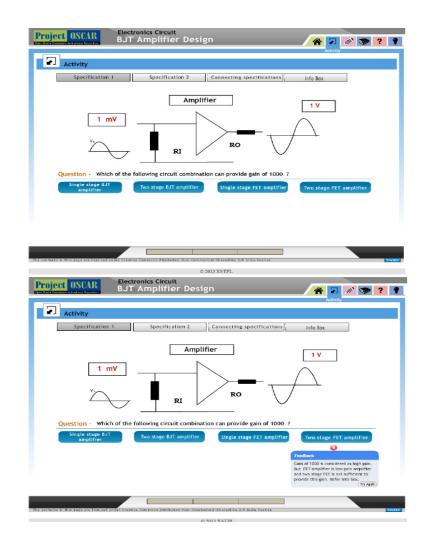

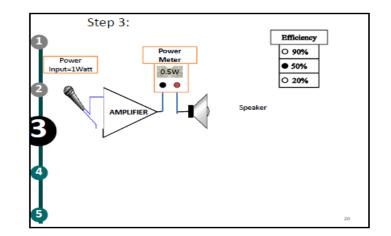

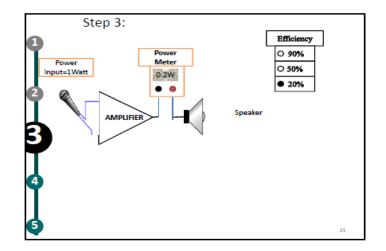

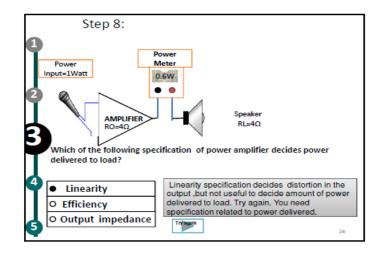

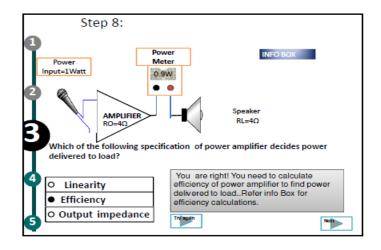

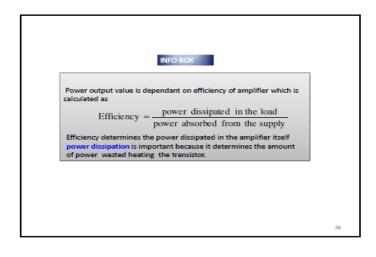

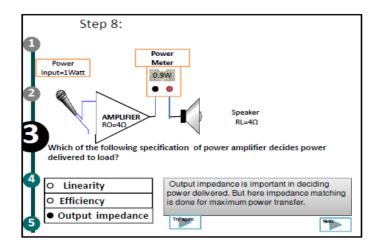

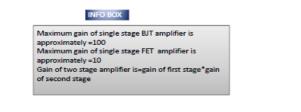

| Fig.  | g. 5.3. Decision Making Task Question (D      | MTQ) Learning Dialog92                            | 2 |

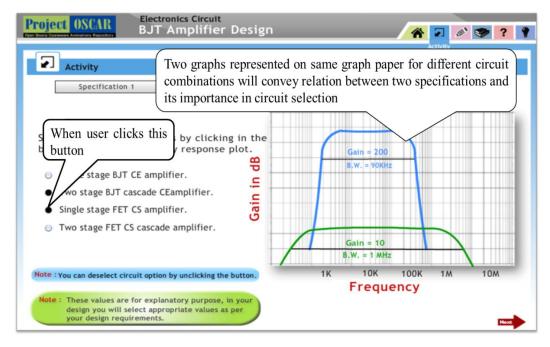

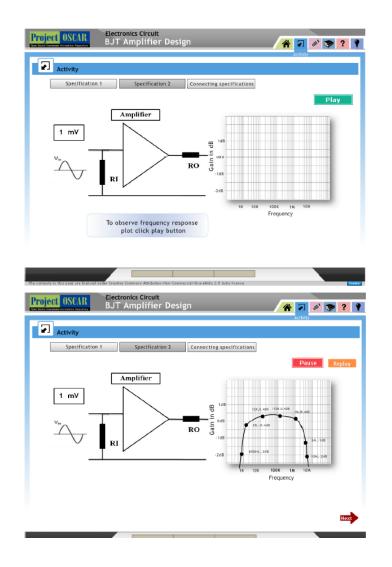

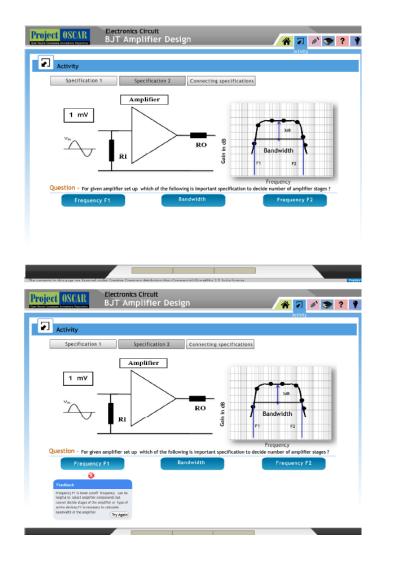

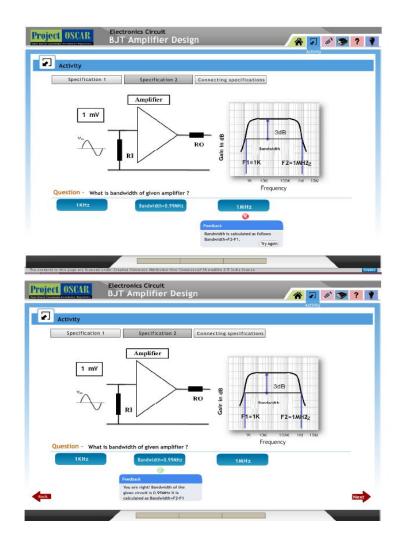

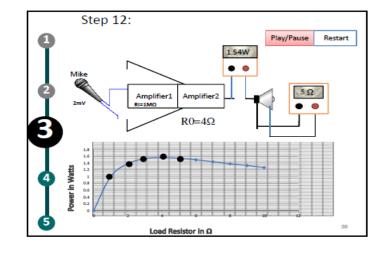

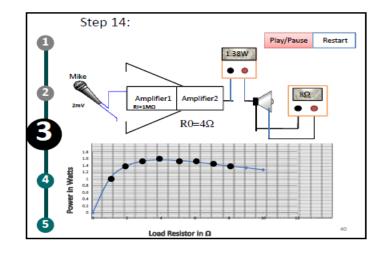

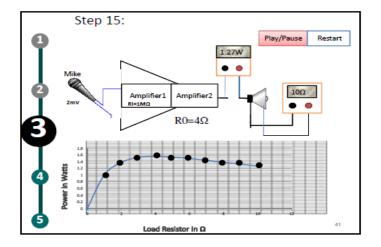

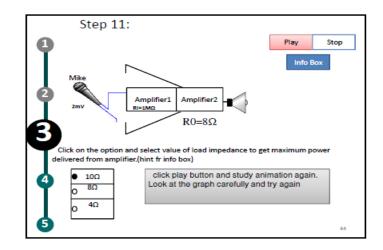

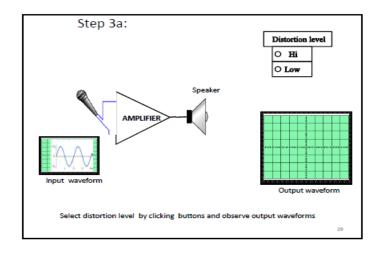

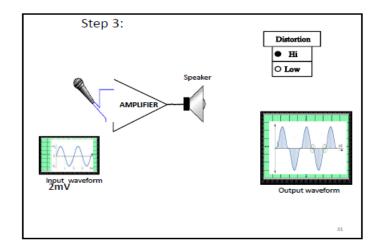

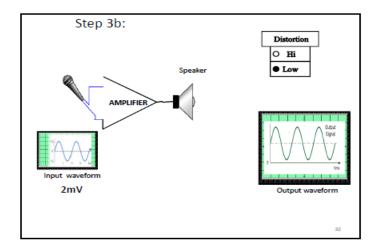

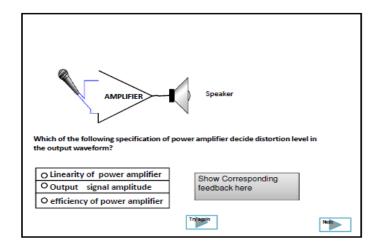

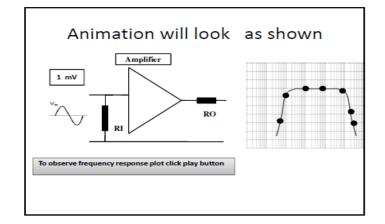

| Fig.  | g. 5.4. Simulative Manipulation Learning      | Dialog93                                          | 3 |

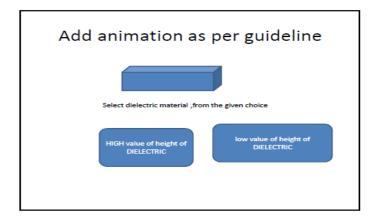

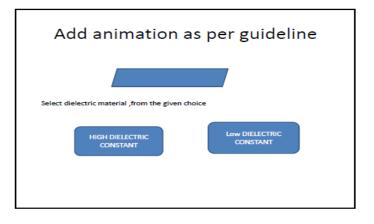

| Fig.  | g. 5.5. Controlled Animation Learning dia     | log94                                             | 4 |

| Fig. 5.6. Concept Clarification Question (CCQ) Learning Dialog                         | 95    |

|----------------------------------------------------------------------------------------|-------|

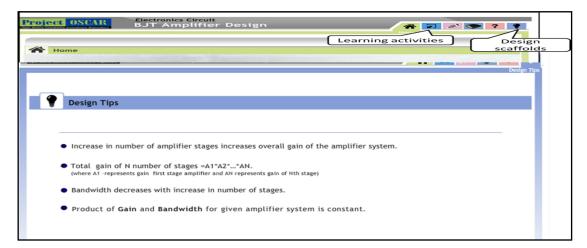

| Fig. 5.7. Capsule Recommendation Learning Dialog                                       | 95    |

| Fig. 5.8. Pedagogical framework to design TEL environment for engineering de           | sign  |

| competencies                                                                           | 97    |

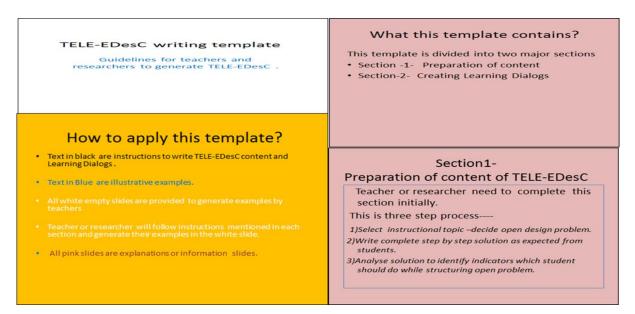

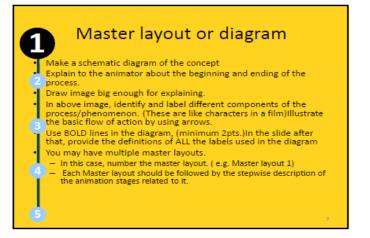

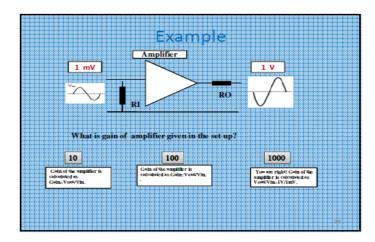

| Fig. 5.9. Slides in the template                                                       | 100   |

| Fig. 5.10. Template slides showing guidelines for Learning Objectives and Learning Dia | logs  |

|                                                                                        | 100   |

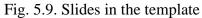

| Fig. 5.11. Flow diagram of Template                                                    | 101   |

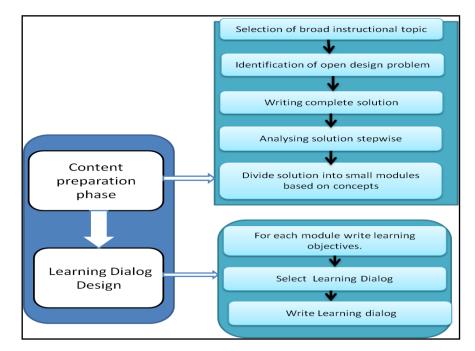

| Fig. 5.12. Process to write learning objectives                                        | 103   |

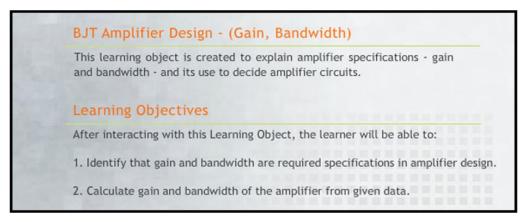

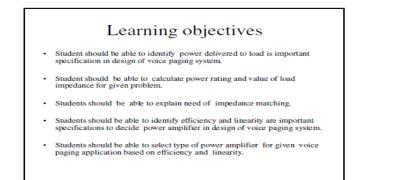

| Fig. 5.13. Example of learning objectives for topic of Amplifier Design                | 104   |

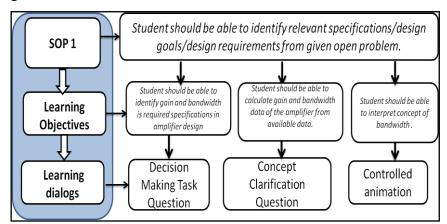

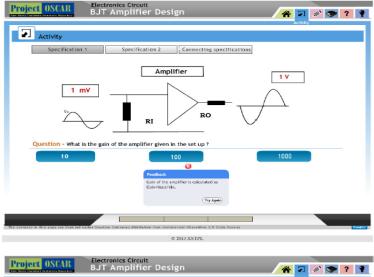

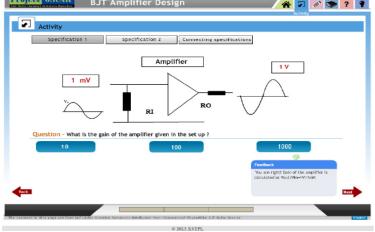

| Fig. 5.14. Learning Dialogs for SOP1 (ref: table 5.5)                                  | 104   |

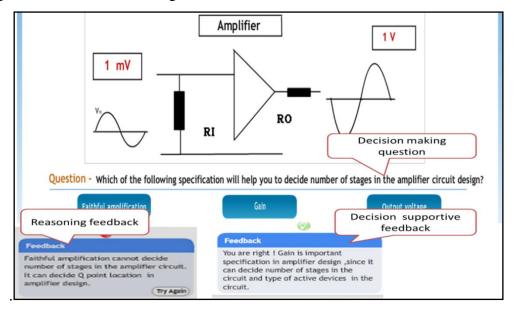

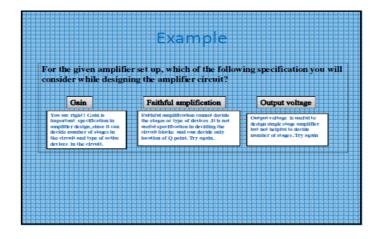

| Fig. 5.15. DMTQ for learning outcome of SOP1                                           | 105   |

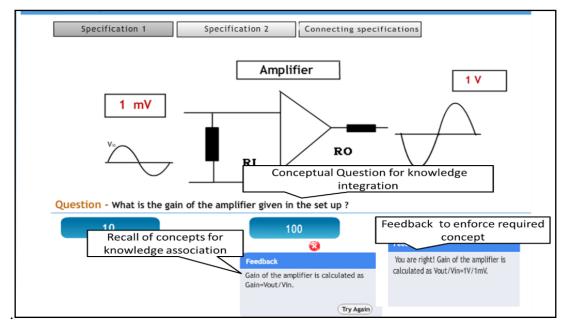

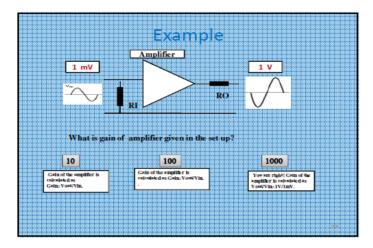

| Fig. 5.16. CCQ for learning outcome of SOP1                                            | 106   |

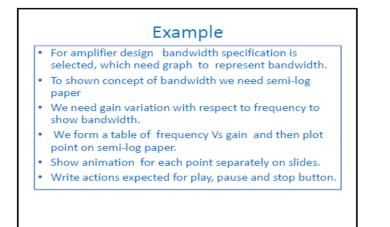

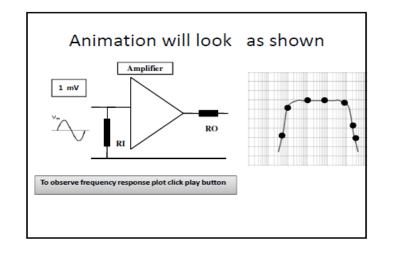

| Fig. 5.17. Controlled animation for SOP1                                               | .107  |

| Fig. 5.18. Learning Dialogs for SOP2 (ref table 5.5)                                   | 107   |

| Fig. 5.19. DMTQ and information agents with example                                    | 108   |

| Fig. 5.20. Simulative Manipulation for SOP2                                            | 109   |

| Fig. 5.21. Learning Dialog for SOP4                                                    | 110   |

| Fig. 5.22. Capsule recommendations (CR) for SOP4                                       | .111  |

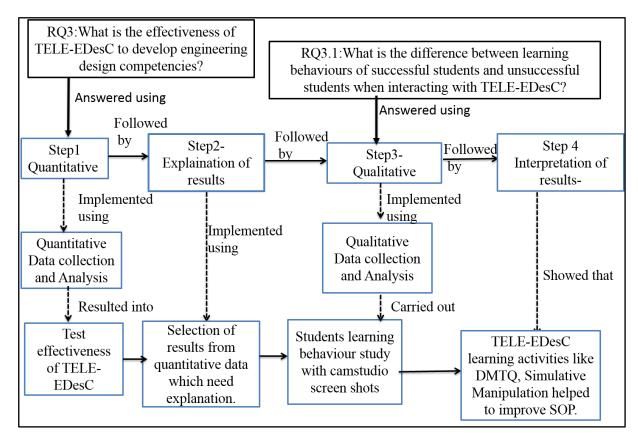

| Fig. 6.1. Steps of sequential explanatory mixed method research design                 | .115  |

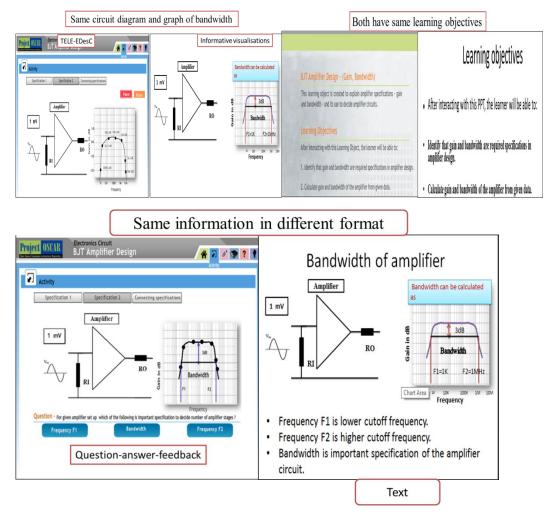

| Fig. 6.2 Similarities and difference beteen TELE-EDesC and Informative visualisations  | .117  |

| Fig. 6.3. Post-test Question for controlled experiment                                 | 118   |

| Fig. 6.4. Frequency plots of rubrics scores for experimental (N=146) and control gr    | roup  |

| (N=149)                                                                                | 121   |

| Fig. 6.5. SAT diagram showing relation between prior knowledge achievement level       | and   |

| success in SOP competency                                                              | 128   |

| Fig. 6.6. Comparison of total time spent on TELE-EDesC activities by successful        | and   |

| unsuccessful students                                                                  | 133   |

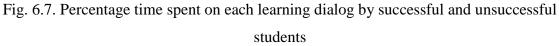

| Fig. 6.7. Percentage time spent on each learning dialog by successful and unsuccess    | ssful |

| students                                                                               | .134  |

| Fig.7.1. Screenshot of TELE-EDesC with self-assessment rubrics                              | .143  |

|---------------------------------------------------------------------------------------------|-------|

| Fig. 7.2. Stratified Attribute Tracking Diagram for successful and unsuccessful design      | .146  |

| Fig. 7.3. Procedure for transfer of SOP competency in new context                           | . 149 |

| Fig. 8.1.Writing learning objectives using template                                         | .157  |

| Fig. 8.2. Learning Dialogs for topic of scheduling developed using template                 | . 158 |

| Fig. 8.3. Pedagogical framework to design TELE-EDesC (reproduced from Ch.5)                 | .161  |

| Fig. 8.4. Example of content analysis of an expert's design actions sub-competency wise.    | .163  |

| Fig.8.5. DMTQ learning dialog for Multiple Representation                                   | . 169 |

| Fig 8.6. Guided Constructor                                                                 | . 169 |

| Fig.8.7.Simulative Manipulation                                                             | . 170 |

| Fig. 9.1. Overview of research questions, methods, results and contributions of this thesis | .188  |

## List of Tables

| Table 1.1. Rubrics items for Structure Open Problem (SOP) competency    5                        |

|--------------------------------------------------------------------------------------------------|

| Table 2.1: Overview of design competency definitions from various researchers         26         |

| Table 2.2. Mapping of competencies from different research papers    28                          |

| Table 2.3. Common TEL environment learning features    42                                        |

| Table 4.1. Design competencies and definition (repeated from relevant columns of Table 2.2).     |

| 61                                                                                               |

| Table 4.2. Design competencies and its sub-competencies                                          |

| Table 4.3. Revision of rubrics item from structure open problem competency         64            |

| Table 4.4. Rubrics items for structure open problem (SOP) competency                             |

| Table 4.5. Types of validity, and its application to engineering design competency rubrics67     |

| Table 4.6. Changes in rubrics items69                                                            |

| Table 4.7. Correlation between design grade and competency scores    72                          |

| Table 4.8. Average Agreement of rubrics scores (statistical significance kappa) for all raters74 |

| Table 4.9. Correlation between SOP sub-competencies                                              |

| Table 5.1. Learning outcomes for sub-competencies    85                                          |

| Table 5.2. Codes and categories for SOP learning outcomes                                        |

| Table 5.3. Instructional strategies for triggering metacognitive processes         90            |

| Table 5.4. TELE-EDesC Learning Dialogs for metacognitive processes of SOP                        |

| Table 5.5. Pedagogical framework to develop TELE-EDesC for "Structure Open Problem               |

| (SOP) competency                                                                                 |

| Table 5.6. Guidelines for content preparation    102                                             |

| Table 5.7. Topics for TELE-EDesC modules from analog circuit domain                              |

| Table 6.1. Comparison of SOP sub-competency ranks    122                                         |

| Table 6.2. Comparison of SOP sub-competency mean scores    123                                   |

| Table 6.3. Comparison of SOP sub-competency ranks for topic of DC circuit design                 |

| Table 6.4. Comparison of SOP sub-competency ranks for topic of Amplifier design                  |

| Table 6.5. Comparison of SOP sub-competency ranks for topic of OP-AMP comparator124              |

| Table 6.6. Performance in SOP sub-competency for low, medium and high achievers in             |

|------------------------------------------------------------------------------------------------|

| experimental group                                                                             |

| Table 6.7. SOP sub-competency in control vs. experimental group, low achievers126              |

| Table 6.8. SOP sub-competency in control vs. experimental group, medium achievers126           |

| Table 6.9. SOP sub-competency in control vs. experimental group, high achievers                |

| Table 6.10. Example of transcript of Camstudio recording                                       |

| Table 6.11. Coding scheme applied to transcript of Camstudio recording.         131            |

| Table 6.12. Spearman rank correlation coefficient between SOP scores and time spent on         |

| different Learning Dialogs (* indicates significance at 0.05 level)134                         |

| Table 7.1. Rubrics for sub-competencies of Structure Open Problem competency142                |

| Table 7.2. Comparison of SOP sub-competency ranks    145                                       |

| Table 7.3. Mean scores for competency acquisition test and transfer test in control group150   |

| Table 7.4. Mean scores for competency acquisition test and transfer test in experimental group |

|                                                                                                |

| Table 7.5. Mean scores and ranks of transfer test scores of control and experimental group.    |

|                                                                                                |

| Table 8.1. Steps and guidelines applied by teachers in content preparation phase               |

| Table 8.2. Learning outcomes for sub-competencies    162                                       |

| Table 8.3. Codes and categories for MR learning outcomes                                       |

| Table 8.4. Instructional strategies for metacognitive processes    166                         |

| Table 8.5. TELE-EDesC Learning Dialogs for metacognitive processes of MR167                    |

| Table 8.6. Framework applied for "Multiple Representations (MR)" design competency 168         |

| Table 8.8. Metacognitive processes for Information Gathering competency                        |

| Table 8.9. Metacognitive processes for Divergent thinking                                      |

| Table 8.10. Metacognitive processes for Convergent thinking    173                             |

| Table 8.11. Comparison of SOP sub-competency mean scores    179                                |

| Table 8.12. Comparison of SOP sub-competency ranks for statistical significance                |

## **Abbreviation Notation and Nomenclature**

| ABET       | Accreditation Board for Engineering and Technology, Inc.          |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|

| CANM       | Controlled animations                                             |  |  |  |

| CCQ        | Concept Clarification Question                                    |  |  |  |

| CDIO       | Conceive, Design, Implement and Operate                           |  |  |  |

| CONV       | Convergent thinking                                               |  |  |  |

| DIV        | Divergent thinking                                                |  |  |  |

| DMTQ       | Decision Making Task Question                                     |  |  |  |

| EDR        | Educational Design Research                                       |  |  |  |

| ICE        | Idea Connection Extension                                         |  |  |  |

| ICT        | Information and Communication Technology                          |  |  |  |

| IG         | Information Gathering                                             |  |  |  |

| MR         | Multiple Representations                                          |  |  |  |

| PBL        | Problem Based Learning                                            |  |  |  |

| SM         | Simulative Manipulation                                           |  |  |  |

| SOP        | Structure Open Problem                                            |  |  |  |

| TEL        | Technology enhanced learning                                      |  |  |  |

| TELE-EDesC | Technology Environment to develop engineering design competencies |  |  |  |

| TIDEE      | Team Design Skill Growth Survey                                   |  |  |  |

## **Declaration Sheet**

I declare that this written submission represents my ideas in my own words and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action by the Institute/the Academy and can also evoke penal action from the sources which have thus not been properly cited or from whom proper permission has not been taken when needed.

(Signature)

<u>Mrs.Madhuri Krishnanand Mavinkurve</u> (Name of the student) <u>10438803</u> (Roll No.)

Date:

## **Chapter 1**

### Introduction

Engineering is a practice profession. Thus, in addition to content knowledge in various topics, engineering students should be able to demonstrate and apply various cognitive or thinking skills such as problem formulation and problem solving, designing and conducting experiments, data analysis and interpretation, design of systems to meet needs and constraints, modelling real-world systems processes, and so on. (Besterfield-Sacre et al., 2000; Shuman et al., 2005). Thinking skills are cognitive processes that human beings apply for sense-making and problem-solving (Beyer, 1988). One such important cognitive or thinking skill for engineering education is engineering design thinking skill (Atman et al., 1999; Dym, 2005). It has been recommended that graduates of engineering programs should be those who can design effective solutions to meet social needs (ABET 2012). In addition, a fundamental objective in undergraduate engineering laboratories is, "Design, build, or assemble a part, product, or system, including using specific methodologies, equipment, or materials; developing system specifications from requirements; and testing and debugging a prototype, system, or process using appropriate tools to satisfy requirements" (Dym, 2005).

As an example, consider a scenario wherein electronics companies manufacture a wide variety of testing equipment. The company hires fresh electronics engineering graduates who are assigned the responsibility of designing a function generator, which is an instrument that produces variety of test signals. In order to design a function generator, the engineer should be aware of its purpose, the waveforms that need to be designed, the amplitude and frequency ranges to be provided and other such requirements. He/she is expected to identify which circuits and block diagrams will satisfy the requirements. The set of thinking skills required to design solutions to such type of problems is the context of this thesis and referred as "engineering design thinking skill".

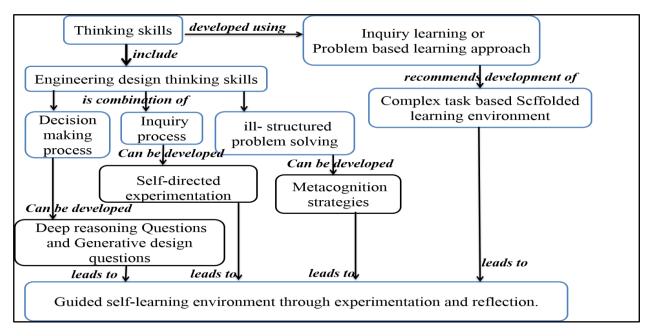

Engineering design thinking skill is a combination of complex cognitive process such as ill-structured problem solving, inquiry learning and systematic decision making (Dym, 2005; Aurisicchio et.al, 2007). The complexity of cognitive process makes it difficult to teach and learn skills.

Engineering design is taught in many universities and institutes as a separate course and based on a version of project-based learning (PBL) (Wilczynski & Douglas, 1995; Benjamin & Keenan, 2006). In PBL-based courses, students are given an open-ended problem for which they need to design products, which are then evaluated (Dunn-Rankin et.al., 1998). Some of the design courses were based on reverse engineering (Wood et.al, 2001) methods of product development. Even though these courses have been reported as useful ones, these courses are resource intensive in terms of faculty time, infrastructure and cost. These courses are project or problem oriented than design thinking skill development.

The above problem is compounded in part because of the lack of a unique definition of what comprises engineering design thinking. Engineering design thinking is perceived in different ways by educationists and researchers. Some consider engineering design thinking as critical steps (Aurisicchio et.al., 2007) to be followed, some perceive it as a problem solving activity (Pahl et al.,1996; Ullman,1988; Gero, 1990), and some consider it as developing competencies (Plonka et.al., 1994).

Another reported challenge in the teaching-learning of engineering design thinking skill is the assessment of students' performance in engineering design courses (Dutson et. al., 1997). Engineering design is an ill-structured, open-ended task. Varied assessment methods are possible and different assessment instruments exist, however there is no standard process or instrument.

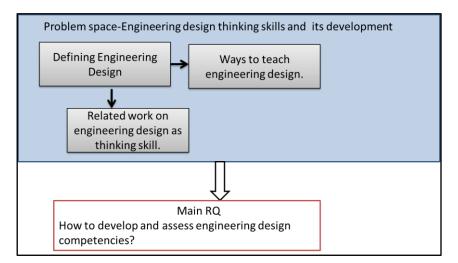

#### **1.1. Problem statement**

The broad problem addressed in this thesis is that of teaching engineering design thinking, which has reported challenges in its teaching and assessment. One approach to address the above challenges of developing as well as assessing complex thinking skills is that of identifying measurable competencies associated with the thinking skill (for example, the competencies defined by ABET for engineering undergraduates (ABET 2000). In this thesis, we take this approach and consider engineering design thinking skill in terms of competencies. Some researchers have taken this approach (Plonka et al., 1994; Crain et al., 1995), but different researchers have addressed the competencies using different terminologies.

To define the specific problem for this thesis, we reviewed existing research to identify engineering design competencies, analysed and mapped the common competencies and synthesized them into a set of competencies which can then form the basis of developing teaching-learning solutions and assessment instruments. The important competencies required for engineering design thinking that emerged from the literature review are: Structure Open Problem (SOP), Multiple Representations (MR), Information Gathering (IG), Divergent thinking (DIV) and Convergent thinking (CONV).

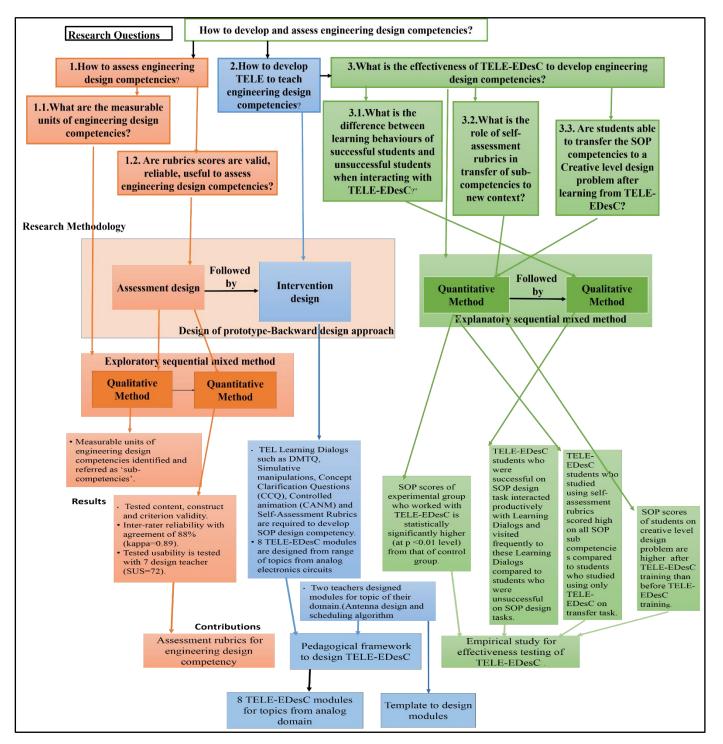

This led to the central research issue addressed by the thesis, i.e. the teaching-learning and assessment of engineering design competencies. The main research question is:

How to develop and assess engineering design competencies?'

#### **1.2. Solution overview**

#### **1.2.1.** Motivation for solution

Learning of thinking skills such as design requires complex learning environments (Hmelo-Silver et al., 2004; Linn, Clark & Slotta, 2003). One approach to developing such learning environments is by harnessing the affordance of modern technology (Reiser, 2004). In recent years, the affordances of ICT have led to the development of technology enhanced learning (TEL) environments to teach various thinking skills. These TEL environments contain affordances such as interactive experimentation (van Joolingen et al., 2005), self-regulation (Azevedo et al., 2010; Molenaar & Roda, 2011), personalized feedback (Reiser, 2004) that provide opportunity to students to perform the required complex cognitive tasks. TEL environments are self-learning and work as supportive training material which will reduce faculty load in design courses.

There exist numerous TEL systems to promote various thinking skills in learners such as modelling ability, scientific reasoning and inquiry skills, argumentation, and virtual experimentation. Notable ones include WISE (Linn et. al. 2003), Co-Lab (van Joolingen et. al., 2005), numerous ones on scientific argumentation (Scheuer et. al, 2010 contains many examples) and Go-Lab (de Jong et al., 2014). Most of these TEL environments focus on middle school and high school levels with fewer for tertiary education, and none explicitly address engineering design thinking skill.

## **1.2.2. TELE-EDesC: TEL Environment for Engineering Design** Competencies

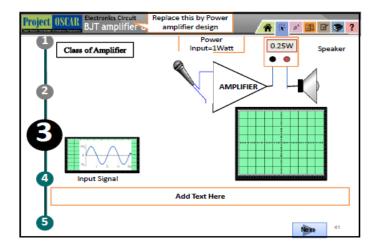

We developed 'TELE-EDesC' (pronounced as "Tele-desk") - a Technology Enhanced Learning Environment to teach Engineering design Competencies. TELE-EDesC contains learning modules with interactive learning actions and activities to be performed by the learner. These are referred as Learning Dialogs.

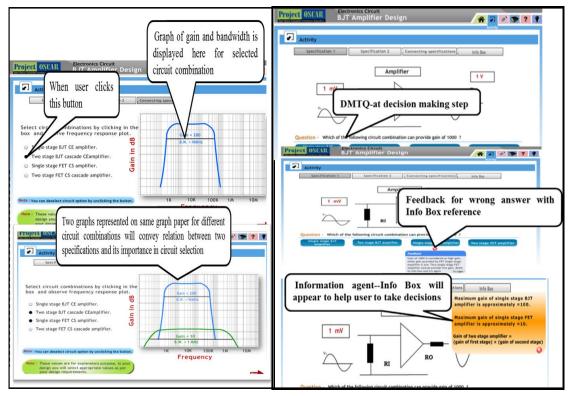

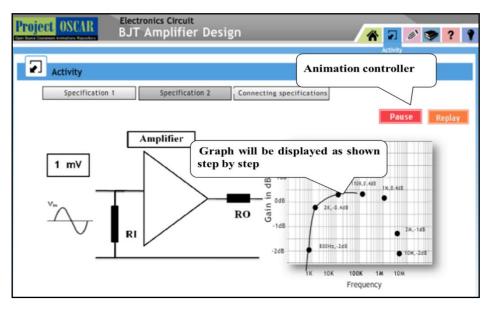

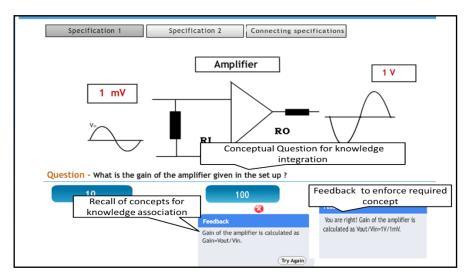

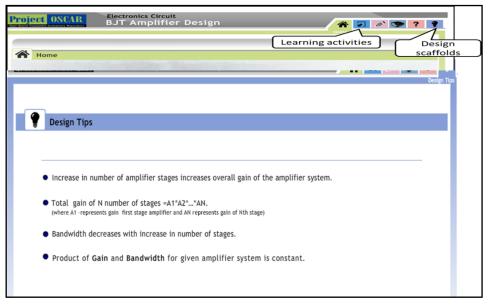

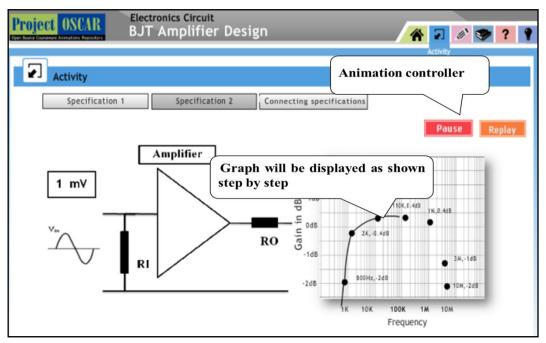

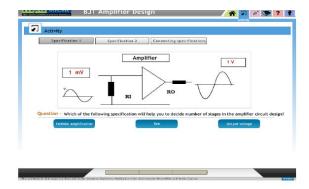

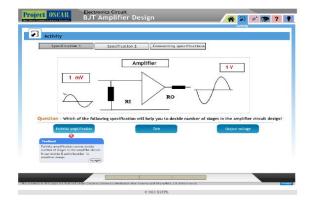

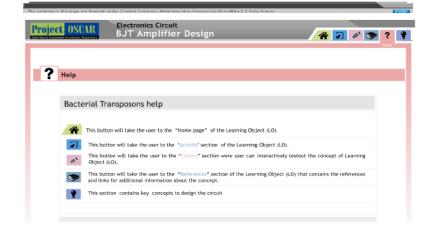

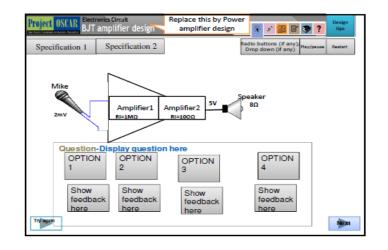

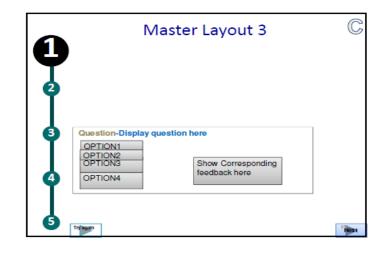

Fig. 1.1. Learning Dialogs of TELE-EDesC

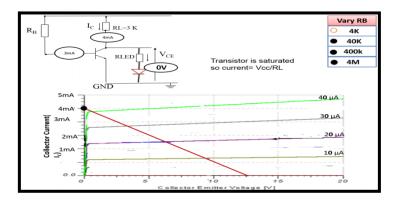

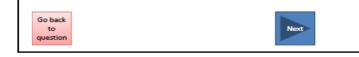

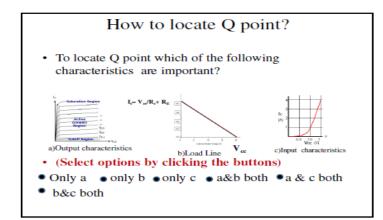

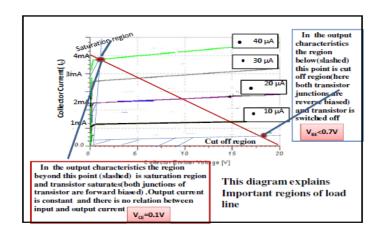

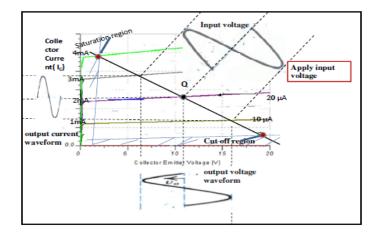

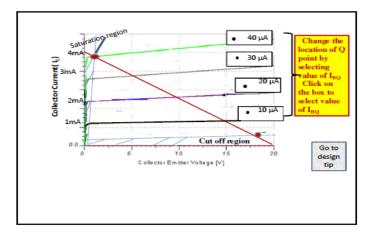

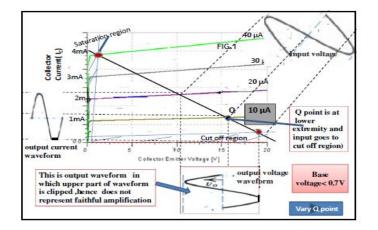

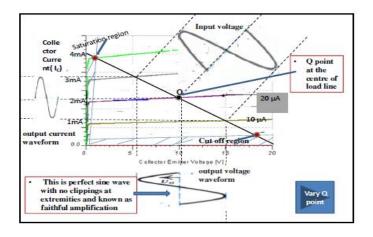

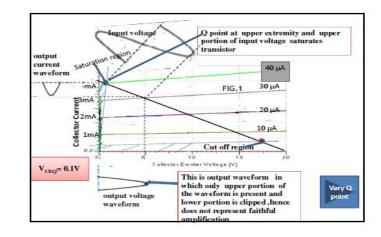

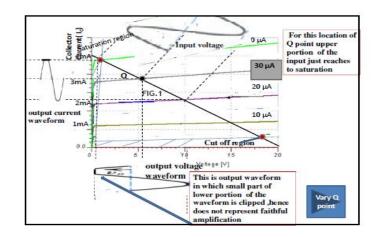

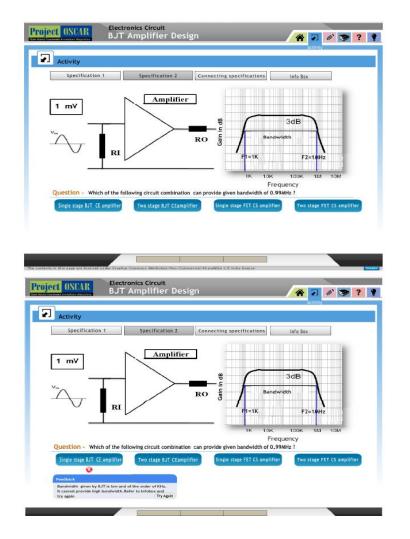

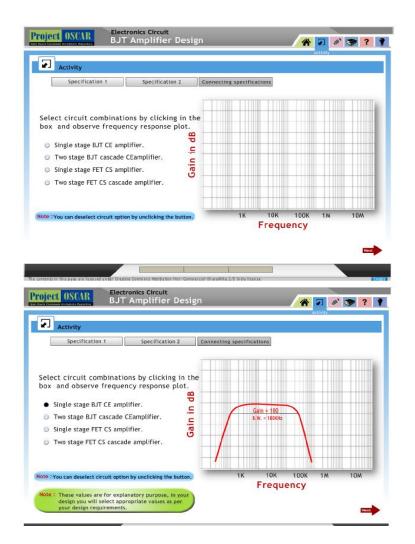

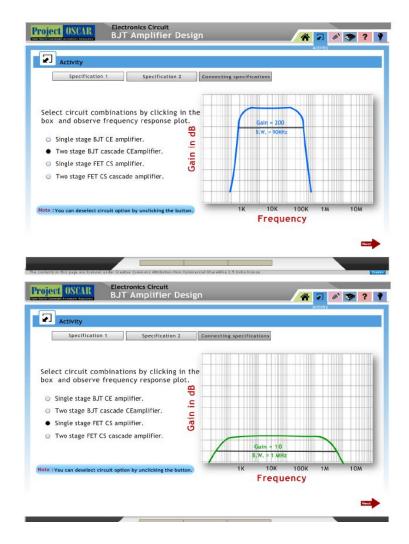

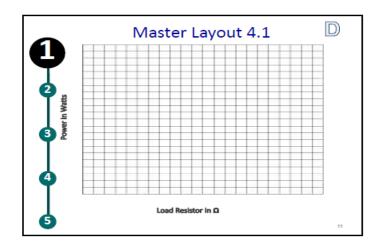

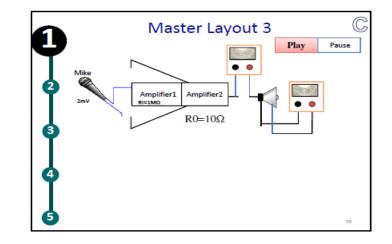

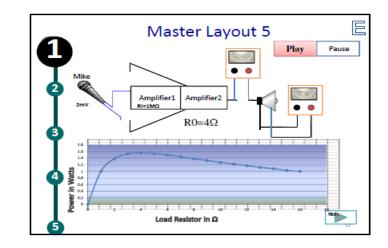

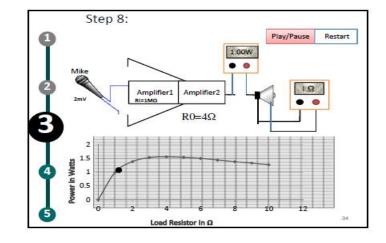

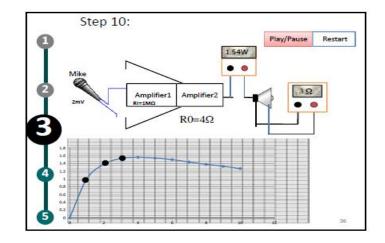

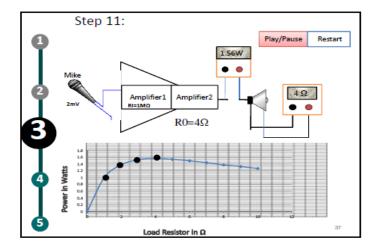

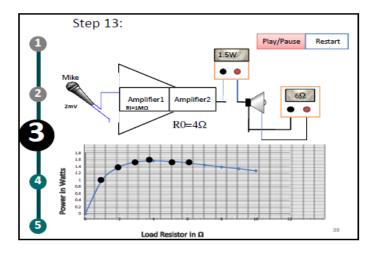

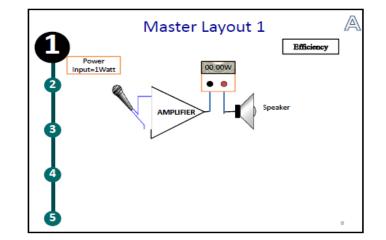

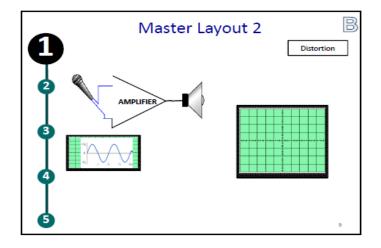

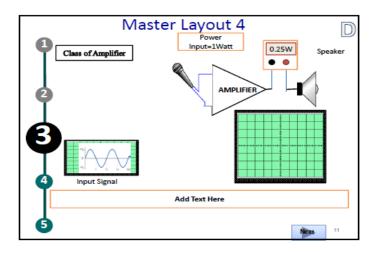

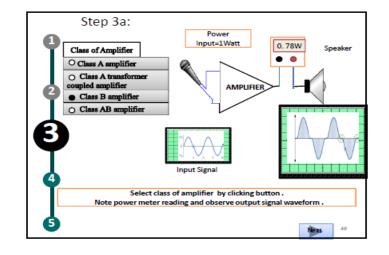

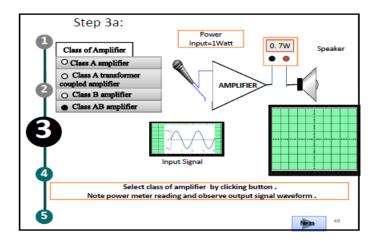

Fig. 1.1 shows an examples of a TELE-EDesC Learning Dialogs to teach the engineering design competency of Structure Open Problem (SOP). We explained Simulative

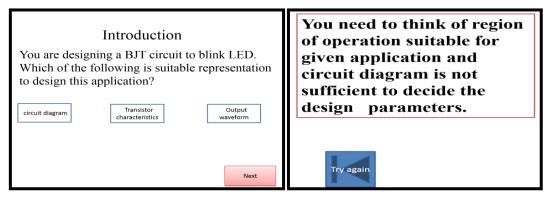

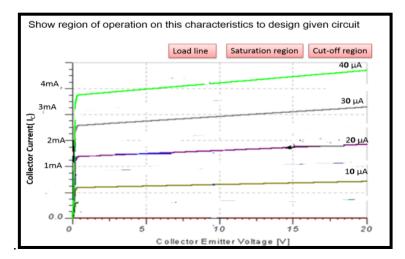

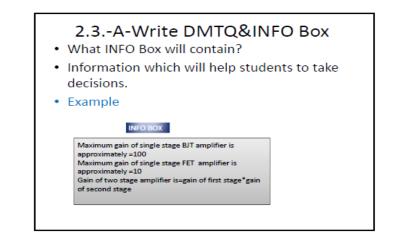

Manipulation (left figure of Fig. 1.1) and Decision Making Task Question Learning Dialogs (right figure of Fig. 1.1) of SOP. In the Simulative Manipulation Learning Dialog shown in the example, learners are provided with control to vary different parameters and explore the variations. In Decision Making Task Questions (DMTQ), guided questions, are provided to reflect on design effectiveness of variations. The call-outs in the figure show components of Learning Dialogs such as graphs, feedback boxes, information box and its role in learning. TELE-EDesC contains variety of such Learning Dialogs to address various engineering design competencies.

In order to assess learners' engineering design competencies, we developed assessment rubrics. Rubrics are descriptive rating scales which consist of pre-established performance criteria to evaluate student's performance or product resulting from performance task (Mertler, 2001). Rubrics have been suggested as a suitable instrument to evaluate open ended activities (Bailey & Szabo, 2007) like design. Rubrics are known for their capacity to enhance deep learning amongst students by providing rich, detailed and specific feedback to students about their performance. Rubrics contain criteria to achieve the competency, target scoring description and intermediate level scoring descriptions. This make process of evaluation transparent to learners. Table 1.1 shows example of rubrics to assess one sub-competency of structure open problem competency.

| Design sub-<br>competency                                                                                     | Target performance                                                                                                                                          | Needs improvement                                                                                                                             | Inadequate                                                                                                                | Missing                                               |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Is able to<br>extract required<br>relevant<br>specifications in<br>detail from<br>given open<br>ended problem | All relevant visible and<br>hidden specifications are<br>identified in detail and<br>interpreted accurately.<br>No irrelevant<br>specifications identified. | An attempt is made to<br>identify specification<br>Most of them identified<br>but few hidden ones<br>missing or needs more<br>interpretation. | An attempt is<br>made but most of<br>the identified<br>specifications are<br>are wrong or<br>irrelevant or<br>incomplete. | No attempt is<br>made to<br>extract<br>specifications |

Table 1.1. Rubrics items for Structure Open Problem (SOP) competency

#### 1.2.3. Approach to designing solution

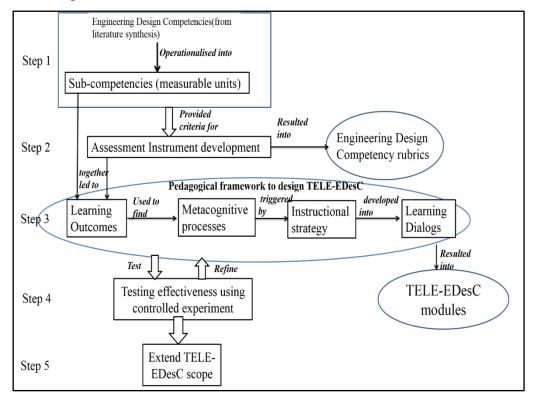

The solution is approached using following steps (Fig. 1.2):

Operationalization of engineering design competencies into smaller measurable units - "sub-competencies".

- Development of the assessment instrument.

- Development of pedagogical framework to design TEL environment, and its application into the TELE-EDesC learning modules.

- Evaluation of TELE-EDesC learning modules in terms of learning effectiveness of design competencies and refinement of modules based on results.

- Extension of TELE-EDesC beyond scope.

These steps are implemented using Education Design Research Method (Van den Akker, 2012) explained in next section 1.3.

Fig. 1.2. Steps of solution approach

#### **1.3. Methodology**

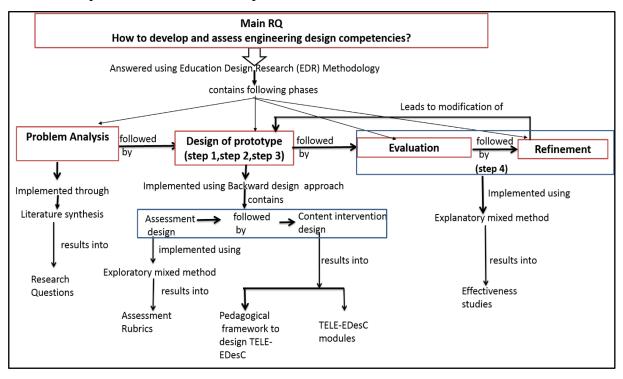

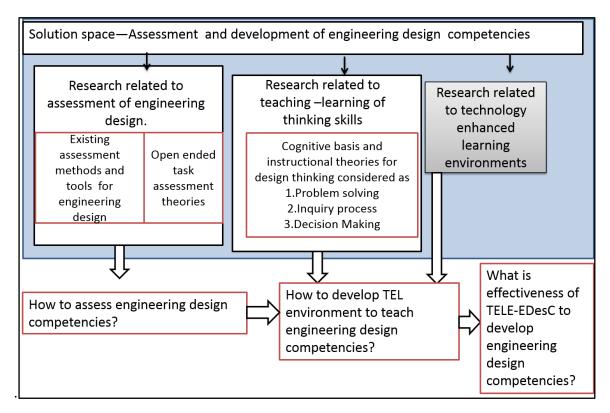

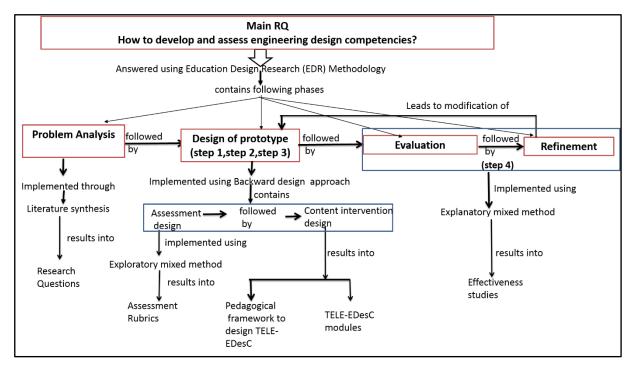

The main research question 'How to develop and assess engineering design competencies?' is answered using Education Design Research (EDR) (Van den Akker, 2012). EDR is "design and development of intervention as a solution to complex educational problem as well as advance knowledge of researchers about the characteristics of intervention." EDR has four phases as problem analysis, design of prototype, evaluation and refinement. The phases are sequentially executed and the outcomes of each phase triggers the next phase (Fig. 1.3). The detailed EDR method is described in Chapter 3, and a summary of its application is given below.

In the first phase of EDR, the problem analysis phase, engineering design thinking skill is characterised as measurable competencies through analysis and synthesis of literature on this topic. In this phase, we also reviewed various assessment methods and instruments for assessing design competencies. We explored instructional methods to teach thinking skills using TEL environments. The problem analysis provided the specific research questions of the thesis as

1) How to assess engineering design competencies?

2) How to develop TEL environment to teach engineering design competencies?

This phase is described in Chapter 2.

Fig. 1.3. Overview of Research Methodology (EDR)

The next phase is design of prototype, which is carried out using backward design approach (Wiggins, & McTighe, 2005), and answers two research questions that emerged from problem analysis phase. Backward design starts by development of the assessment method followed by design of content intervention. In order to develop instrument we applied exploratory sequential mixed method design.

The development of the assessment instrument for engineering design competencies begins with the process of identifying and defining the specific competencies. Engineering design competencies identified from literature are broadly defined, and lead to multiple possible learning outcomes. Thus it is necessary to operationalize these competencies to small measurable units, which we refer as sub-competencies in this thesis (Step 1, Fig. 1.2). Sub-competencies form the basis of the expected learning outcomes and the assessment criteria. We developed descriptive performance rubrics to assess design competencies based on the sub-competencies of engineering design. We tested the validity, reliability, and usefulness of rubrics (Step 2, Fig. 1.2). The product developed is "Assessment rubrics for engineering design competencies".

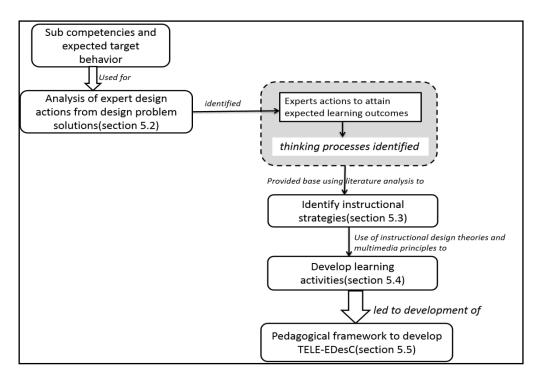

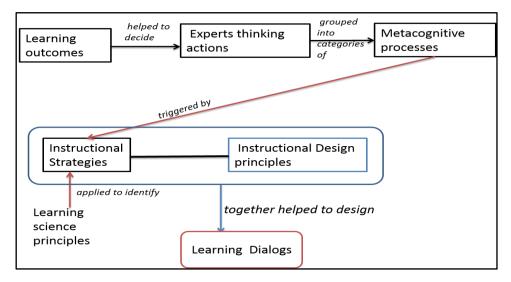

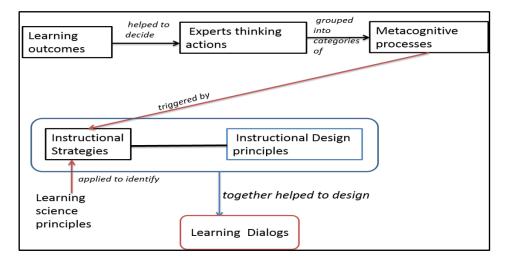

Sub-competencies together with rubrics target criteria provided learning outcomes for design competencies. Learning outcomes are applied to develop TELE-EDesC Learning Dialogs. In order to design Learning Dialogs, we followed the approach shown in Fig. 1.2 (Step 3). We first identified metacognitive process to be triggered by using experts thinking action in the design problem solution. Instructional strategies to trigger these metacognitive processes are identified from literature review. Learning Dialogs of TEL environment are designed based on instructional strategies using Instructional Design principles of interactive learning environment. This systematic approach is referred as 'pedagogical frame work to design TELE-EDesC'. This framework is applied to identify Learning Dialogs of TELE-EDesC for SOP competency. This framework provided TELE-EDesC modules of our study.

This 'design of prototype 'phase of EDR (design of prototype) contributed to assessment instrument rubrics, pedagogical framework to design TELE-EDesC and TELE-EDesC learning modules. This phase of EDR covered first three steps mentioned in the solution approach in Fig. 1.2. Research methodology details of this phase are described in Chapters 4 and 5.

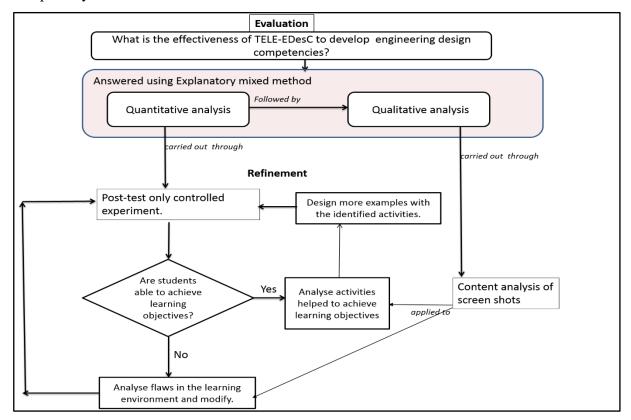

The last phase of EDR is evaluation and refinement, which is carried using explanatory mixed design method. In this method quantitative analysis is followed by qualitative analysis. Controlled quasi-experiments with quantitative analysis are conducted to determine the

effectiveness of TELE-EDesC learning module. The learning behaviour of students is studied qualitatively. Depending on effectiveness results, the intervention, i.e. TELE-EDesC learning modules are refined. This is carried out iteratively, till students achieve desired competence level. This is fourth step of solution approach (Fig. 1.2). This phase contributed to empirical studies of effectiveness testing for TELE-EDesC. Detailed research method is described in Chapters 6 and 7.

In the final step of solution approach we tested possible extension of our solution beyond scope (Section 1.4). This step is described in detail in Chapter 8.

#### **1.4.** Delimitations of the thesis

Engineering design education and developing related design competencies are broad areas. This section describes the delimitations of this thesis in terms of the scope of content of TELE-EDesC learning modules, the scope of engineering design competencies for which the solutions in this thesis are designed, and the scope of the type and level of design problems addressed.

#### **1.4.1. Scope of content**

In this thesis, we have developed TELE-EDesC learning materials to teach design competencies within the context of an Electronics Circuits course, which is part of a four-year undergraduate engineering programme in all universities. This course is a foundation course taught at the second year level. Electronics circuits and its design find application in almost all streams of engineering. We have selected topics from the course which have been shown to be important in electronics system design. The major concept selected is amplifier design involving varied but primary concepts, on which design of most electronics circuits depends. Topics include circuits for audio frequency and power amplifier so that students learn to design small signal and large signal amplifiers. The above topics consider both linear region of operation which use active devices such as Bipolar-junction transistors (BJT) and Field Effect transistors (FET) as well as non-linear region of operation which uses OPAMP as the active device. A large range of analog electronics circuits are covered by these topics. Amplifier design problems also cover a range of specifications depending on variety of applications. This in turn will prepare students to design various practical systems.

#### 1.4.2. Scope of design competencies

Students' ability of engineering design is described in terms of competencies such as Structure Open Problem, Multiple Representation, Information Gathering, Divergent and Convergent Thinking which are all required in the process of design. Each of these competencies is further broken down into sub-competencies. The solution in this thesis consists of three main components – assessment rubrics for engineering design competencies, a pedagogical framework for designing TELE-EDesC modules for engineering design competencies, and TELE-EDesC learning modules for specific engineering design competencies in specific topics.

- Assessment rubrics are designed for each engineering design competency listed above (Chapter 4). In order to do so, sub-competencies are identified for each competency, which form the basis of the rubrics.

- 2) Pedagogical framework (Chapter 5) to design TELE-EDesC modules. The detailed framework is developed for Structure Open Problem (SOP) competency. After the framework is applied to design TELE-EDesC learning modules for SOP, which are then evaluated, an attempt is made to extend the framework to other engineering design competencies (Chapter 8).

- 3) TELE-EDesC learning modules. The majority of learning materials developed in this thesis, that is TELE-EDesC learning modules, are to develop the competency of Structure Open Problem. This competency is chosen as the first step of design is to structure the given design problem, which is often open-ended. Structure Open Problem is reported to be a key competency for engineering design since substantial part of design activity is devoted to structuring and formulation of problem (Cross, 2007), and poor structuring of problem leads to poor design of artefacts (Atman, 1999). All TELE-EDesC modules for SOP competency are empirically tested in this thesis.

#### **1.4.3.** Scope of design problem type

Engineering design problems are classified as routine, innovative and creative (Brown & Chandrasekaran, 1989).

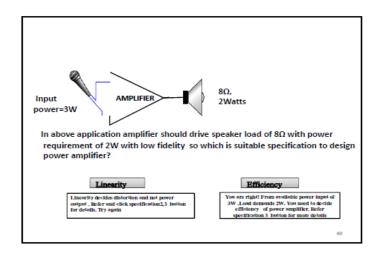

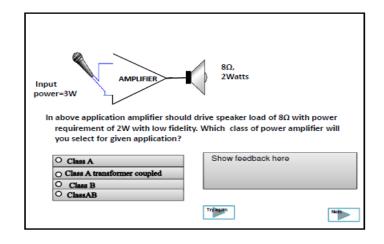

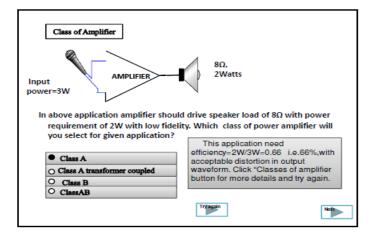

In routine design problems, the effective problem decomposition is known. In electronics circuit design problems, effective decomposition of problem means all specifications are known. In routine problems mapping of sub-functions into physical components is clear, that means type of circuits suitable to meet given specifications are mentioned in the problem. The only task is to select appropriate components that optimise well established criteria. This problem is solved using fixed formulae. Designer will decide appropriate formula to be used and calculate component values and select practical values. Decision making scope is limited to selection of practical components for design. For example, "*Design class –B push pull amplifier to deliver power of 2Watt to 8ohm load*".

In this problem type of power amplifier is known so students will recall the circuit. The power rating and load is given so they will calculate appropriate currents, voltages and will select components in the circuit.

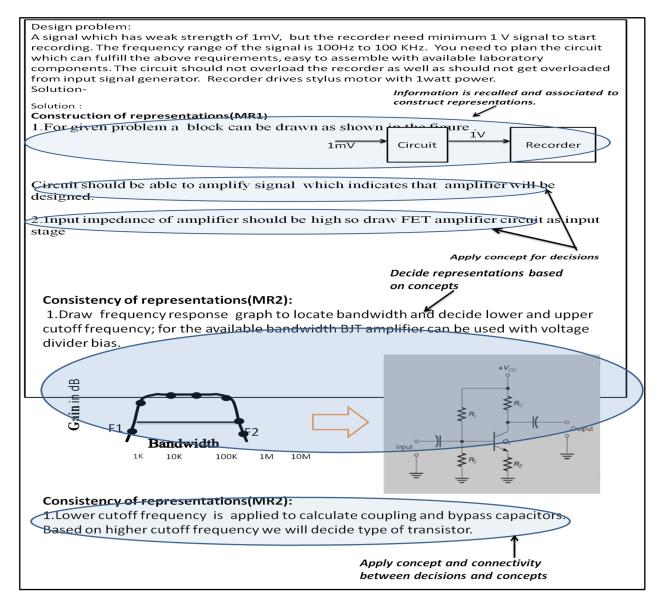

**Innovative design problems** are semi-structured. The top level functional decomposition is known, this means type of circuits like amplifier, filter etc. are mentioned. But physical realisation of sub-functions require considerably more efforts this means designer need to extract all relevant specifications for given application and decide which type of filter or amplifier is suitable in the given application. In this type of problems real world problem is given and multiple solutions are possible. For example "*Design power amplifier to amplify audio signal for paging announcement of supermarket with speaker rating of 8 watt*".

For this type of problems specifications need to be identified by designer and multiple circuits are possible based on identified specifications. Designer need to compare these circuits based on characteristics.

In **creative design problems**, the functional specifications are open ended, effective decomposition is not known and designer need to evaluate multiple options. In these types of problems students can explore variety of solution ideas and analyse pros and cons of proposed

ideas "Design an amplifier for a rock musician who needs to perform in an open-air theatre in front of an audience of a thousand people".

The learning activities developed in this thesis focus on innovative design problems. The goal in all modules of the learning environment is to guide students to structure open innovative design problems. In addition, in one final study (Chapter 8) we tested the extent to which students who learn with TELE-EDesC modules are able to apply their design competencies to the higher creative level problem.

#### **1.5.** Contributions of the thesis

The major thesis contributions are:

- Eight TELE-EDesC modules have been developed for four topics for Structure Open Problem competency, in a range of problems that cover major topics in analog electronics circuit domain.

- Assessment rubrics for engineering design competencies have been developed and validated. The following have been established: content, construct and criterion validity, interrater reliability and usability.

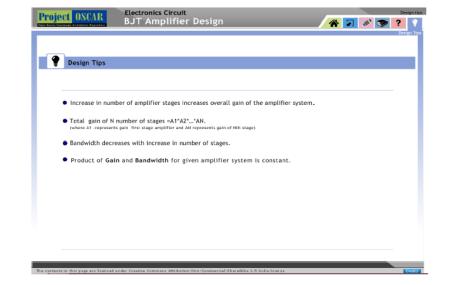

- A pedagogical framework to design TELE-EDesC modules for developing students' engineering design competencies has been proposed and tested. The framework provides the steps to researchers to develop Learning Dialogs of a TEL environment for developing students' engineering design competencies. In particular, the framework prescribes specific Learning Dialogs (and guidelines to create them) for SOP competency Decision Making Task Questions (DMTQ),Simulative Manipulations, Concept Clarification Questions (CCQ),Self-assessment rubrics, Controlled Animation (CANM),Capsule Recommendations (CR) and Information Box(Info Box)

- Effectiveness study of TELE-EDesC learning modules using quantitative and qualitative analysis is conducted. This study confirmed that Learning Dialogs prescribed by the framework are required to develop Structure Open Problem design competency.

The minor contributions of this thesis are:

- Important competencies and sub-competencies for engineering design thinking have been identified and operationalized into measurable learning outcomes, for domain of analog electronics circuits.

- A template is developed for teachers, content creators of TEL environments, and researchers to design TELE-EDesC modules for SOP in their respective domains. Template contain specific guidelines to prepare content and write Learning Dialogs.

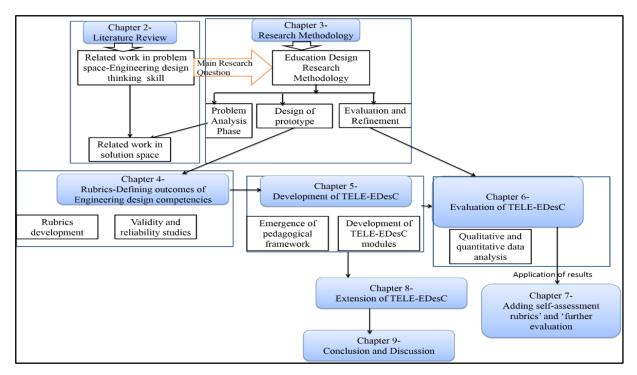

#### 1.6. Organization of the thesis

This thesis is organized as follows. In Chapter 2 related work is reviewed, from which the research questions emerge. Chapter 3 describes the overall research methodology applied. Chapter 4 presents the development and validation of assessment instrument rubrics. Chapter 5 serves a two-fold purpose: it describes the emergence of the pedagogical framework to design TELE-EDesC modules, and demonstrates the application of the framework to design learning modules for SOP competency. Chapters 6 presents the evaluation of TELE-EDesC modules, followed by the application of its results in Chapter 7 to refine TELE-EDesC modules. Chapter 8 describes possible paths of extension of the solution boundaries. Chapter 9 concludes the thesis with a summary and discussion of research questions, exploration of possible future directions. Fig. 1.4 shows organisation and connections of the thesis chapters.

Fig. 1.4. Thesis chapters' organisation and connections

## **Chapter 2**

### **Literature Review**

In Chapter 1, we presented an overview of the research in this thesis that included a brief reference to the literature contributing to the problem of developing engineering design skills. In Chapter 2, we critically analyse and synthesize literature to identify the gaps in existing work and unaddressed research issues. We describe the various areas in which we surveyed existing research, and the reasons behind selecting these areas. This chapter builds the reference framework for design of the TELE-EDesC learning environment to develop engineering design competencies among students. It also provides guidance for the choice of the methodology for the study.

### 2.1. Organisation of literature review

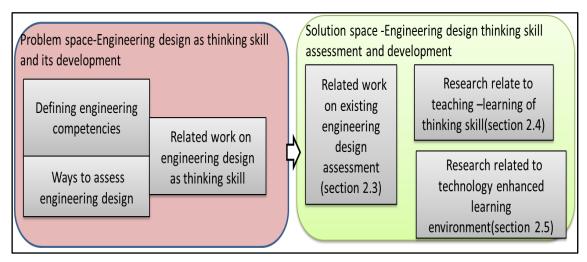

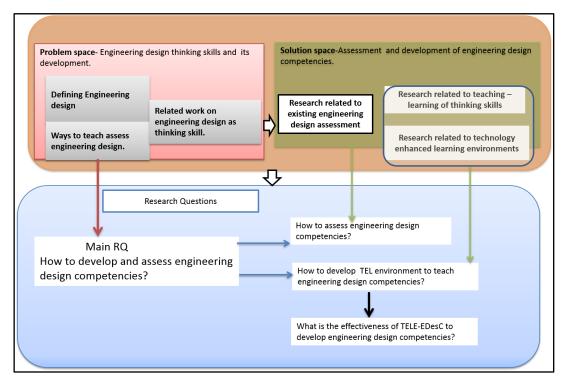

The literature reviewed in this chapter is organized into themes that form the framework for the 'problem space' and the 'solution space' of this thesis (Fig. 2.1).

Fig. 2.1. Organisation of related work

We begin the review of literature by surveying different existing ways to teach engineering design. We review the theories underlying engineering design thinking and report the effectiveness of various education methods in terms of the attainment of design competencies by students. In Section 2.2, we describe the parental theory that formed the background of the research problem, that is, what is engineering design. The parental theory contains features of the design thinking process and methods to develop competencies through curriculum or instructional strategies. The analysis of literature on instructional and assessment methods for design education led to the main research problem of the thesis: 'How to develop and assess engineering design competencies?'

We follow a 'backward design' (Wiggins &McTighe, 2005) approach and first focus on the assessment of engineering design competencies. Engineering design is an open-ended task and varied assessment methods are possible. The task complexity further increases when decisions need to be taken for what to assess. Section 2.3 reviews different methods to assess and evaluate students design tasks. The literature review for this section leads to the identification of a suitable approach to assessing engineering competencies, and the need for developing a valid and reliable instrument for doing so.

The next part of the literature review focuses on the solution theories related to the development of engineering design thinking skills. Section 2.4 contains a broad review of solution strategies to develop various thinking skills related to engineering design. In Section 2.5, we explore the features and teaching-learning strategies in technology enhanced learning environments to develop thinking skills and the major components of these technology enabled learning environments.

#### 2.2. Problem space – What is engineering design thinking?

The development of engineering design thinking skill among students is an important goal of engineering education. Professional organizations, accreditation bodies (ABET, 2014) as well as educators (Sheppard, 2003) have emphasized that graduating students should be able to design effective solutions for given needs. However, design thinking is complex and teaching design has been reported to be difficult (Dym, 2005). This section presents the theories underlying engineering design thinking, various methods that are in use to teach

engineering design to students, and conceptualizing engineering design in terms of thinking skills (Beyer, 1988).

#### 2.2.1. Defining engineering design thinking

There is lack of a unique definition of what comprises engineering design thinking, and plenty of definitions and perspectives of engineering design thinking abound (Atman, Chimka, Bursic, & Nachtmann, 1999; Crain, Davis, Calkins, & Gentili, 1995). However, what is common in all approaches is that engineering design is a systematic process, in which "designers generate, evaluate, and specify concepts for devices, systems, or processes" (Dym, 2005). The process of engineering design thinking is a systematic and intelligent decision-making process, through which products or artefacts are generated. These artefacts should be as per specifications or customer requirements and need to satisfy constraints. The steps in the design process may start from the problem definition, progress through conceptual design development and end with testing and verifications. The common pattern of activities during design thinking is summarized as generation, evaluation and decision making (Aurisicchio, Ahmed, & Wallace, 2007).

Engineering design thinking is complex cognitive process that results into an openended creative task (Dym, 2005). The outcomes of the design process can be predicted and thus the engineering design thinking process is deterministic (Dym, 2005). However, during the design process, many divergent ideas are evoked which also shows the element of randomness in the process. Some researchers have described design as a series of activities and they proposed prescriptive models for these activities (Asimov, 1962; French, 1985; Pahl, Beitz, Feldhusen & Grote, 2007).

In summary, engineering design thinking overall is systematic process, but expects internalisation of complex cognitive inquiry with divergent ideas and systematic decision steps.

#### 2.2.2. Methods to teach engineering design

Engineering design is an ill-defined domain. Its definitions vary from a systematic process (Pahl et.al, 2007; Ullman, 1988; Gero, 1990) of solving open-ended problems, to a creative, innovative and unpredictable process (Dym, 2005). This makes design education itself as an open-ended problem with multiple and diverse opinions about teaching design (Dutson, Todd, Magleby & Sorensen, 1997). Even though design educators have differing opinions, they commonly agree to the fact that design helps in converting knowledge into practical experience (Dutson et al., 1997; Wood, Jensen, Bezdek & Otto, 2001). In universities worldwide, most existing engineering design courses were developed based on principles of providing real world problem solving experience to students (Wood, et al., 2001; Dutson, et al., 1997; Dally & Zhang, 1993). Various approaches are used to teach design ranging from systematic sequential learning activities to open-ended activities. The focus of this section is on the teaching-learning of these courses, from both the teacher's perspective on conduction of design education and students' perspective as value addition for their future development.

Design education mostly started with open-ended problem posing and development of solution to real world problem. One of the first approaches to teaching design was through senior capstone courses (Dutson et al., 1997) and provided an experiential learning activity to students. These courses gave an opportunity to convert analytical knowledge gained in previous courses into hands-on projects in final years. These were full scale projects with extensive use of engineering laboratories, prototypes were designed to solve real world problems. The instructional method was typically project-based learning (Kjersdam & Enemark, 1994) and duration of capstone courses varied from a half semester to two semesters. Faculty members conducted supportive lectures to teach concept of design methods, process, risk evaluations, project management, etc. Limitations in such approaches include the cost in terms of infrastructure, and equipment. The cost can be lowered by assigning small scale projects with limited set of specifications. However, this approach brought its own challenge in terms of increased instructor involvement. Case study methods to teach design are implemented in some universities. In this method, projects are discussed

and analysed by faculty members and students. The cost of conduction of this method is very low, but students lack practical design experience (Burton & White, 1999).

Design contests are another method to conduct these capstone courses and products evaluated by peers as well as industry panels provided real time feedback. One of the variants in design courses was experimental designs (Young, Yarranron, Bellehumeur & Svrcek, 2006), and applied to chemical engineering laboratory courses. Students were taught fundamentals related to unit operations in theory classes. They designed and conducted experiments, proposed the processes, collected and interpreted data and justified the results. Effectiveness of the course was described through student's comments. In general these courses were valuable for deeper understanding and provided hands on experience on the field. The subjective evaluation of these courses indicated that teacher and students both appreciated the teaching learning values of these courses. They agreed that such courses helped to connect engineering theory knowledge to hands on practical experience. But in most of the cases cost of conduction was high due to special infrastructure equipment requirements, budget and extra faculty time and effort.

Other approaches include project based learning (PBL), focusing mainly on product development process. PBL approaches have shown positive learning gain (Kolodner et al., 2003) but again the conduction of these courses was time-consuming (Burton & White, 1999; Benjamin & Keenan, 2006). Another approach to teach design was based on reverse engineering (Wood et al., 2001) and known as product evolution or redesign. Reverse engineering is defined as in-depth analysis of existing product to find process of product development and design decisions (Gabriele, 1994). Instructional activity of the course is divided into three phases as reverse engineering, modelling, analysis and redesign. Reverse engineering phase leads to identification of specifications and development of hypothesis, design modelling phase helps to understand design principles of dissected product. Redesign leads to development of the product based on improved specifications. These courses helped students for hands on practical experience and addressed different learning styles of students. The major drawback reported was time commitment from students and they struggled with iteration of design projects (Wood et al., 2001).

Another approach suggested is integration of design across the curriculum (Wilczynski & Douglas, 1995) to develop design thinking process sequentially. Design experience was introduced at entry level considering background and skills of students and revisited throughout the engineering education and ended with true real world design experience of capstone courses. These courses aimed to develop design abilities gradually. Students appreciated the design experience of these courses. The major concern of these types of courses was faculty overload in terms of selection of design problems, addressing student's queries and evaluation of results.

Engineering design in industry is another approach (Dunn-Rankin et al., 1998) which helped teachers and students to learn together the application of engineering fundamentals to industry problems. The course provided opportunity for students to deal with true industry problem and faculty role is not problem poser but partner in problem solution. This process even added value to faculty learning in the way of inquiry method of problem solving. Similar to other capstone courses this course also faced inherent challenges related to cost and faculty overload. But additional challenges included in these courses were bringing companies to campus, protecting confidentiality of projects of the companies and so on.

All the approaches described till now are based on product development through open ended problem solving or sequential teaching learning process of problem solving through learning activities. A different approach to teach design is based on CDIO initiatives and standards (Benjamin & Keenan, 2006). CDIO stands for conceiving, designing, implementing and operating real world systems and products. Multiple Design-Build-Test (DBT) modules were designed for all years with increased level of complexity. Learning outcomes for each DBT module was guided by Bloom's taxonomy. The integrated nature of the modules helped students for immediate application of concepts learnt in theories. These courses helped to acquire professional skills and attributes as well. These courses require extensive involvement of instructors as mentor and metacognitive coaches. Faculty need to keep track of individual team member's skill attainment as well as group project evaluation. Interim feedback from instructor is utmost important for effectiveness of such courses. All these courses were reported to be time consuming and resource intensive (Benjamin & Keenan, 2006; Wood et al., 2001). Assessment of the student's performance is an integral part of teaching learning process. Since engineering design is an ill-structured open-ended activity, assessment of students' performance in design courses has been reported to be another challenge (Dutson et al., 1997; Wood et al., 2001). There exist a variety of methods and criteria that have been used to assess students' performance in engineering design courses (a detailed review is provided in Section 2.3). However, there is no standard procedure or criteria or instrument to assess achievement of students engineering design thinking skill.

The approaches described in this sub-section focus on courses in engineering curricula to teach and assess design. These courses have been reported to be effective and beneficial to students, especially in promoting student interest and retention (Wood et al., 2001). However, challenges have been reported too in running such face-to-face courses, such as extra faculty time, special training, and lack of assessment techniques. Faculty members need to devote lot of time as course designers, mentors, metacognitive coaches and evaluators. Robust assessment criteria and instruments is another challenge. Thus design courses are not common in universities, which translate into lack of design ability among students (Eckerdal et al., 2006; May & Strong, 2011).

In order to overcome these challenges one of the possibilities can be to develop engineering design as a thinking skill progressively through training sessions instead of conducting semester long design course focusing mainly on product development. In next sub-section we explore engineering design from the perspective of a thinking skill.

### 2.2.3. Engineering design as a thinking skill

Thinking skills are cognitive processes that human beings apply for sense-making and problem-solving (Beyer, 1988). These cognitive processes are ill-structured tasks and need to be taught to learners. But after training learners can apply these processes and perform these tasks which indicate that these skills may be transferrable. Thinking skills in science and engineering include experimental design, systems thinking, multiple representations, problem-posing, algorithmic thinking, scientific modelling, feasibility analysis, estimation, graphicacy, evidence collection, and data representation and analysis. Thinking skills are pan-domain in nature, that is, they involve a set of common foundational cognitive processes which cross

boundaries of domains and have applicability across domains. Researchers have characterized pan-domain thinking skills in a variety of ways, such as trans-disciplinary habits of mind (Mishra, Koehler & Henrikson, 2011), ABET student outcomes (ABET, 2012), science process skills (Padilla, 1990), scientific abilities (Etkina et. al, 2006), 21st Century skills (Pellegrino & Hilton, 2012), computational thinking skills (Wing, 2011; Grover & Pea, 2013) and so on.

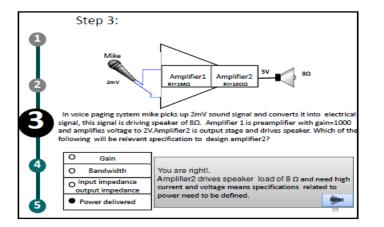

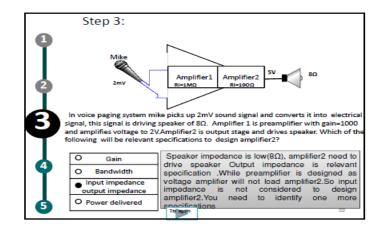

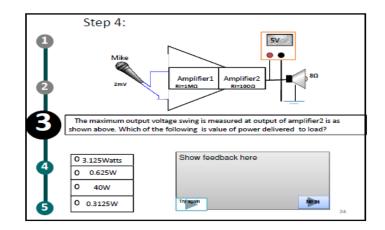

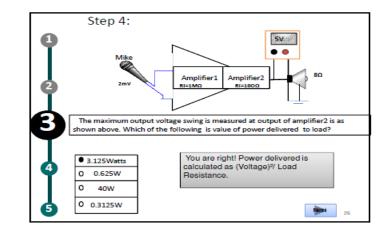

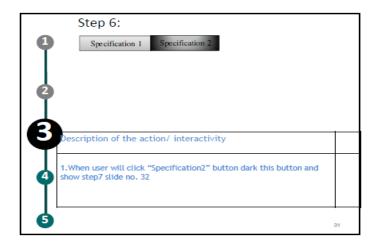

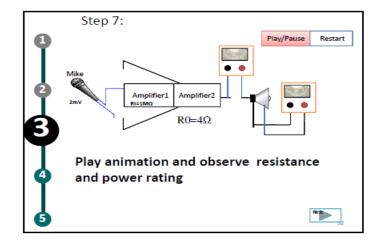

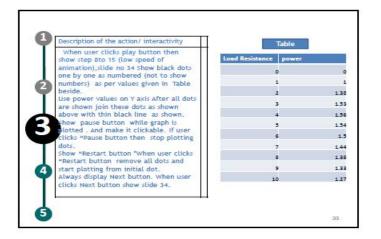

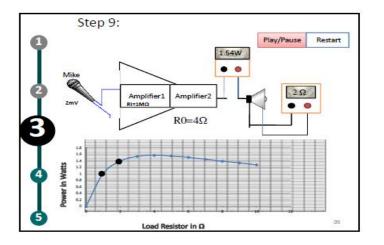

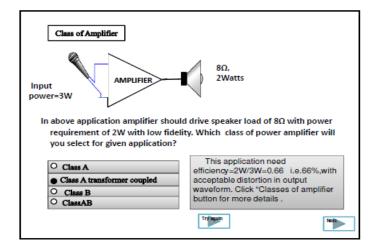

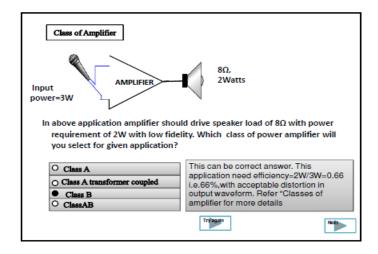

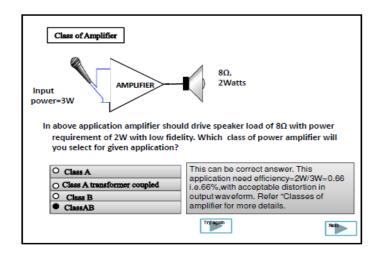

ABET student outcomes for engineering education (ABET, 2014) are defined in terms of a graduating student's abilities such as ability to identify and formulate problems, analyse and interpret data, ability to use modern tools etc. One of the expected outcomes of engineering education according to ABET is that "students should be able to solve open ended design problems". Thinking skills important to the learning of fundamental sciences have been labelled as 'science process skills' (www.narst.org) and include students' basic abilities to observe, draw inferences, think of ways to measure, classify into various categories, predict and test the outcomes and so on. Advanced scientific thinking skills expect students to identify variables, formulate hypothesis, gather and interpret data, operationalize variables, and conduct and analyse experiments. Another categorization scheme of thinking skills in the sciences is 'scientific abilities' which are "important procedures, processes, and methods that scientists use when constructing knowledge and when solving experimental problems" (Etkina et al., 2006). These include the ability to represent a scientific process in multiple ways, design experimental investigations, devise, test and modify a qualitative explanation or a quantitative relationship, collect and analyse data, evaluate conceptual claims and problem solutions and communicate. It is expected that students should apply scientific abilities reflectively, critically and deliberately while attempting scientific experiments or problems.